Rx mac, Rx mac –18 – Altera Interlaken MegaCore Function User Manual

Page 44

4–18

Chapter 4: Functional Description

Receive Path

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

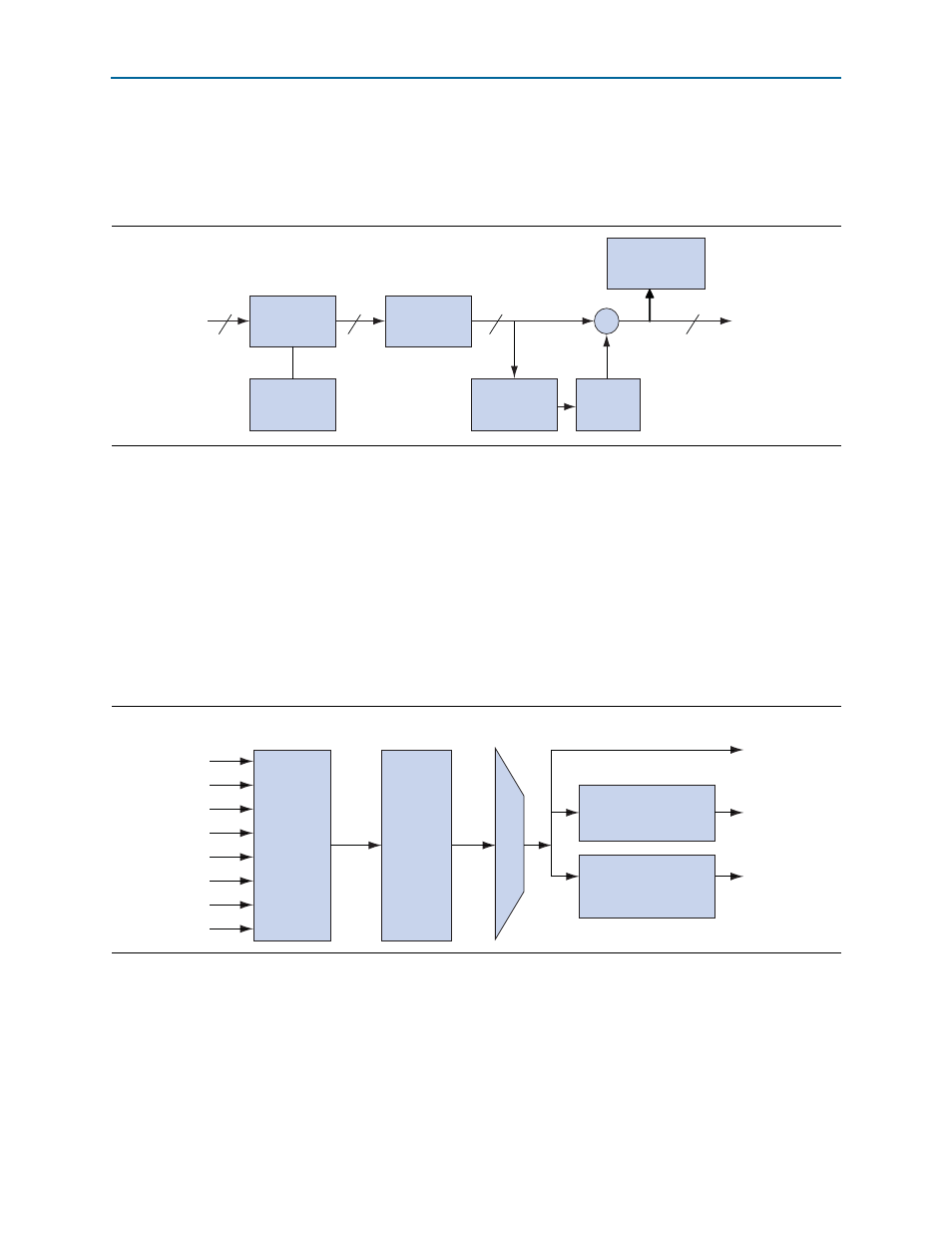

shows the flow through the RX PCS block. The width of the output from

this block is 65 bits; the most significant bit is an Altera-defined control bit that

indicates whether a word is a control word or a data word. The control bit has value 1

if the current word is a control word, and value 0 if the current word is a data word.

RX MAC

To recover a packet or burst, the RX MAC takes data from each of the PCS lanes and

reassembles the packet or burst. The MSB of the incoming data is on lane 0. For more

information about the correspondence between lane numbers and data bit order, refer

to

The RX MAC then validates the CRC-24 bits, and recovers the in-band flow control

calendar bits. It sends the calendar bits to the calendar and status block, and sends the

raw data it retrieves to the RX channel filtering blocks.

shows the flow

through the RX MAC block.

Figure 4–13. Data Flow Through Interlaken MegaCore Function RX PCS Block

Gearbox

67

65

20

Descrambler

CRC32

+

65

Word Aligner

67/64 Decoder

Framing Scheduler

Figure 4–14. Data Flow Through Interlaken MegaCore Function RX MAC Block

Destriping

Lane Alignment

Lane

Aligner

FIFO

Buffer

Calendar Recovery

Block

CRC-24 Validation

Block