Interlaken interface status signals, Interlaken interface status signals –3, Table 5–2 on – Altera Interlaken MegaCore Function User Manual

Page 55: R to, Table 5–2

Chapter 5: Signals

5–3

Interlaken Interface and External Transceiver Interface Signals

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

Interlaken Interface Status Signals

describe the Interlaken interface status signals. These signals

are available whether or not you turn on Exclude transceivers.

ref_clk

Input

Main transceiver reference clock. Refer to

Recommended Frequency and Source”

.

cal_blk_clk

Input

Calibration clock for transceiver on-chip termination resistors. The Stratix IV GX

transceiver on-chip termination resistors are calibrated by a single calibration

block, which requires a calibration clock. The frequency range of cal_blk_clk

is 10–125 MHz. For more information, refer to the

chapter in volume 2 of the Stratix IV Device Handbook.

tx_coreclkout

Output

Master TX clock from transceiver block 0. Clocks the transmit lanes of all

transceiver blocks internally.

rx_coreclkout

Output

The physically central clock from among the rx_clk clocks output from the

transceiver blocks. Drives the common_rx_clk input clock to all transceiver

blocks internally. You can use this clock to drive the rx_mac_c_clk input clock.

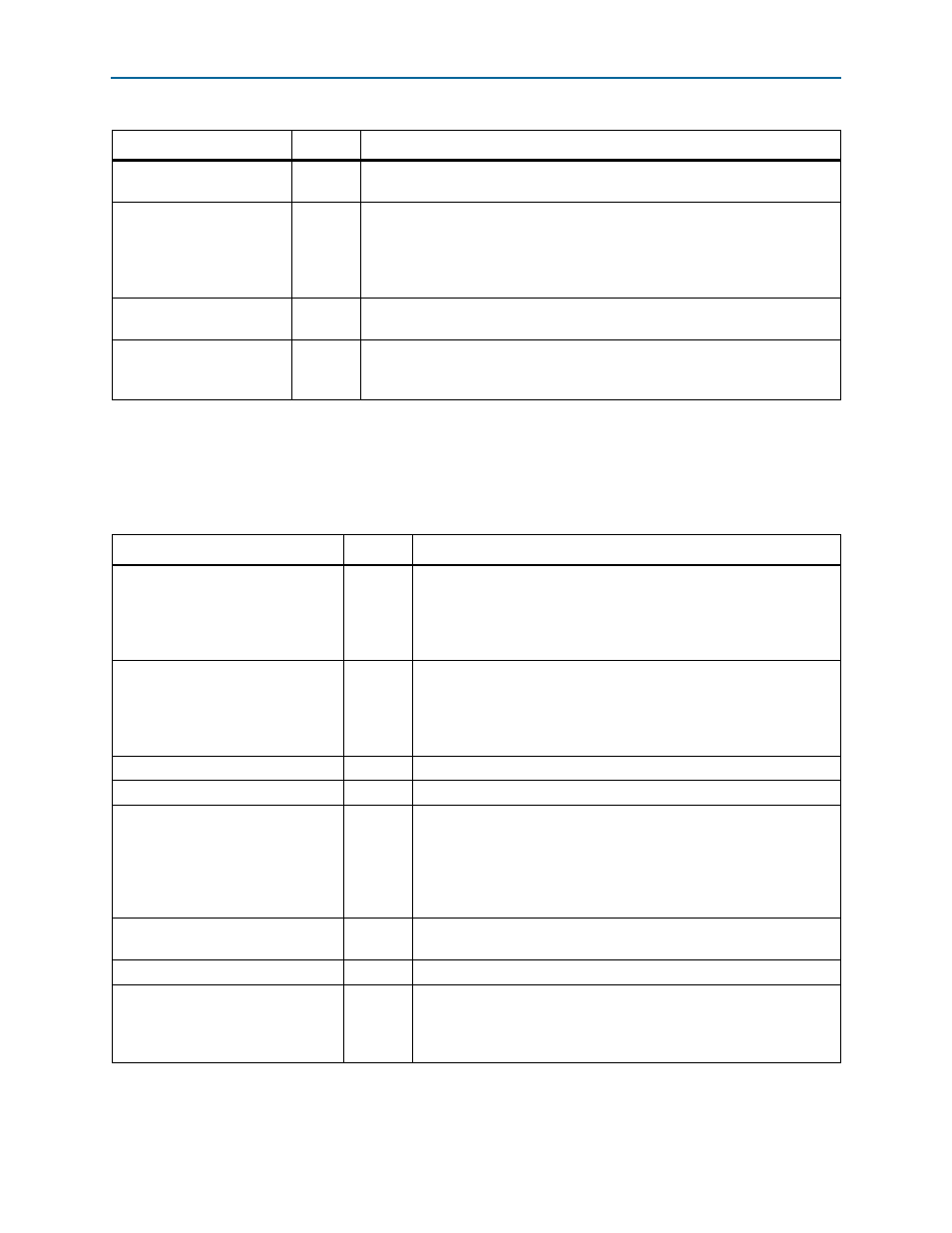

Table 5–1. Interlaken Data Interface Signals (Part 2 of 2)

Signal

Direction

Description

Table 5–2. Interlaken RX Status Interface Signals

(Part 1 of 2)

Signal

Direction

Description

rx_status_per_lane_word_lock

[L:0]

Output

Indicates lane has locked onto the three-bit synchronization header.

(Sixty-four consecutive legal sync patterns have been observed;

64B/67B Word Lock, in the Interlaken specification). This signal is

deasserted when lane word lock is lost according to the Interlaken

specification. Width is the number of lanes (L = num_lanes – 1).

rx_status_per_lane_sync_lock

[L:0]

Output

Indicates lane has locked onto the meta frame boundary and recovered

the scrambler seed from incoming traffic. (Rx LaneValid in the

Interlaken specification). This signal is deasserted when sync lock is

lost according to the Interlaken specification. Width is the number of

lanes (L = num_lanes – 1).

rx_status_all_word_locked

Output

Indicates all lanes are word-locked.

rx_status_all_sync_locked

Output

Indicates all lanes are sync-locked.

rx_status_fully_locked

Output

Indicates the Interlaken receiver is fully locked. This signal is asserted

when rx_status_all_word_locked is high,

rx_status_all_sync_locked

is high, and lane alignment is

complete. (RX Operational, in the Interlaken specification). The signal is

deasserted when any of these three conditions no longer holds,

according to the Interlaken specification.

rx_status_locked_time[15:0]

Output

Counter that tracks the time elapsed since rx_status_fully_locked

is asserted. Increments once every 318 × 10

6

rx_mac_c_clk cycles.

rx_status_error_count[15:0]

Output

Counter that tracks the number of CRC-24 errors encountered.

rx_status_per_lane_crc32_errs

[Q:0]

Output

Per-lane, 8-bit counters for tracking the number of CRC-32 errors

encountered. Width is 8 × num_lanes. (Q = 8 × num_lanes – 1).

Bits[7:0] track the CRC-32 errors on RX lane 0, bits [15:8] track the

CRC-32 errors on RX lane 1, and so on.