Altera Interlaken MegaCore Function User Manual

Page 34

4–8

Chapter 4: Functional Description

Clocking and Reset Structure

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

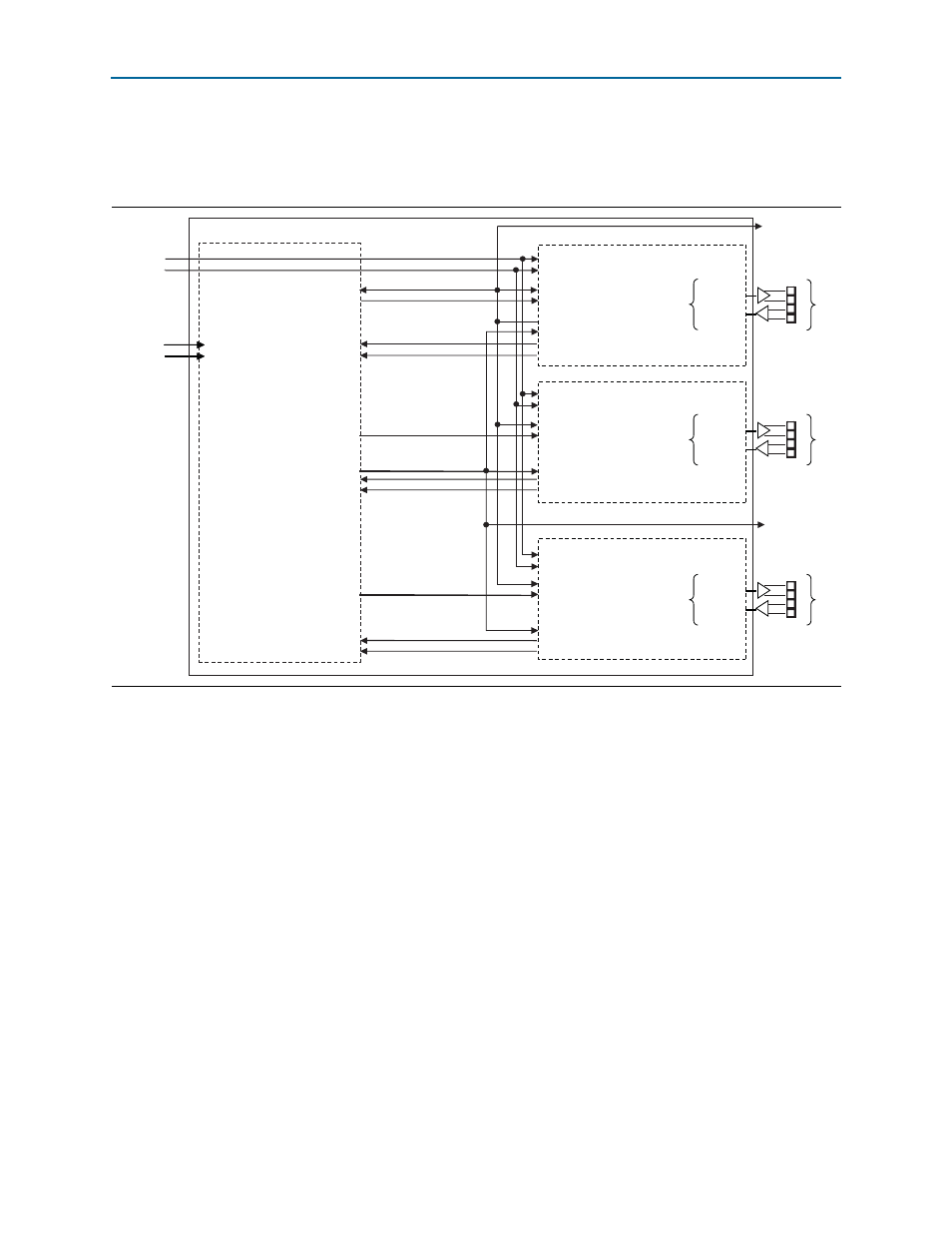

shows the clock diagram for a 12-lane, 6-Gbps variation. In this variation,

the transceiver datapath width is 20. The clock diagram for a 12-lane, 10-Gbps

variation is identical, except that the transceiver datapath width is 40.

Figure 4–5. Clock Diagram for 12-Lane, 6-Gbps Interlaken MegaCore Function

cal_blk_clk

ref_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

tx_lane_clk

tx_data [79:0]

tx_data [159:80]

rx_data [79:0]

rx_lane_clk [3:0]

rx_data [159:80]

rx_lane_clk [7:4]

common_rx_coreclk

tx_data [239:160]

rx_data [239:160]

rx_lane_clk [11:8]

HSIO Bank 0

(low latency PCS mode)

tx_coreclkout

rx_coreclkout

x4

tx_mac_clk

rx_mac_clk

tx_mac_clk

rx_mac_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 1

(low latency PCS mode)

x4

cal_blk_clk

ref_clk

clk_in

Lanes 0 to 3

tx_datain[79:0]

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 2

(low latency PCS mode)

Lanes 4 to 7

Lanes 8 to 11

x4

TX MAC and PCS

RX MAC and PCS