Arbiter, Arbiter and application behavior, Arbiter –12 – Altera Interlaken MegaCore Function User Manual

Page 38: Arbiter and application behavior –12

4–12

Chapter 4: Functional Description

Transmit Path

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

Arbiter

The channel arbiter arbitrates between the two incoming channels, channel 0 and

channel 1, using a round-robin arbitration scheme. It implements an Avalon-ST

interface in communication with the channel, with one important modification that

involves the tx_chX_datain_empty signal.

Arbiter and Application Behavior

In the round-robin arbitration scheme, if data is available on both channels and the

Interlaken IP core is not backpressuring either channel, the arbiter accepts data from

the two channels on alternating cycles. The application can enforce full packet mode

operation by forcing each channel to wait until the other channel completes sending a

packet before it asserts its own valid signal. You can use the

tx_control_channel_enable[1:0]

bits to selectively disable a channel temporarily.

The channel width depends on the Interlaken MegaCore function variation. Both

channels have the same width.

shows the channel width for each supported

variation.

The arbiter asserts the tx_chX_datain_ready signal to indicate it is ready to receive

new data on channel X. The application indicates to the arbiter that valid data is

available on channel X by asserting the tx_chX_datain_valid signal and holding

valid data on tx_chX_datain_data. The arbiter reads data when both

tx_chX_datain_valid

and tx_chX_datain_ready are asserted.

shows an example of the required behavior.

1

The application should hold tx_chX_datain_valid and current data values on

tx_chX_datain_data

steady for a full tx_mac_c_clk clock cycle in which both the

valid and ready signals are asserted, because otherwise the arbiter does not read this

data. The application need not wait for the ready signal to be asserted before

presenting the initial data to the tx_chX_datain_data bus and asserting the valid

signal.

The channel deasserts its valid signal when it has no more valid data to present on

tx_chX_datain_data

. It must maintain the current data on the data bus while it

asserts the valid signal, until one full clock cycle after the arbiter asserts the ready

signal. This behavior is compliant with the Avalon-ST interface specification with

ready latency 0.

f

For more information, refer to the

.

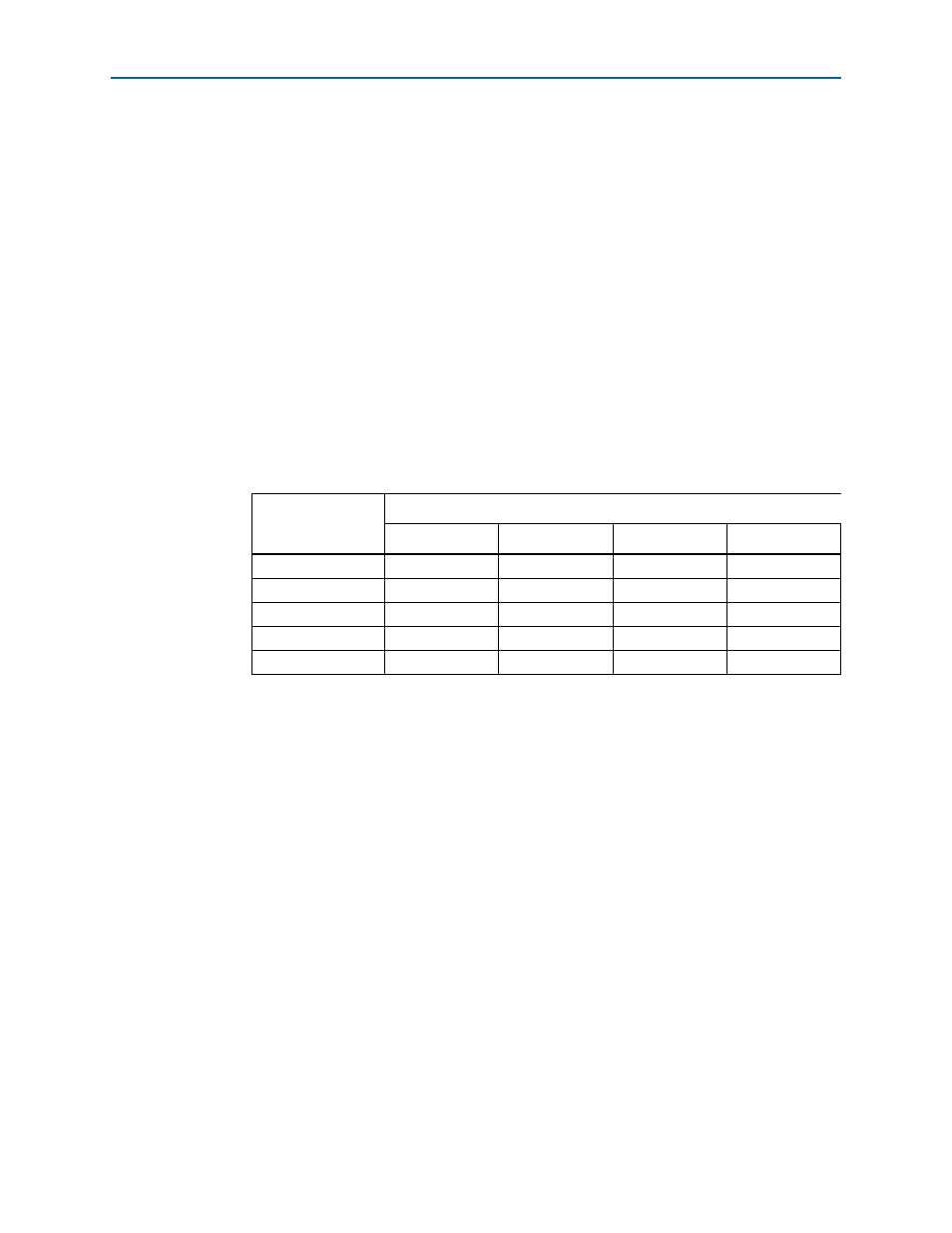

Table 4–5. Application Channel Width in Bits for Supported Variations

Number of Lanes

Lane Rate (Gbps)

3.125

6.25

6.375

10.3125

4

128

128

128

—

8

128

256

256

—

10

—

256

256

—

12

—

256

256

512

20

—

512

512

—