Pcs clock frequencies – Altera Interlaken MegaCore Function User Manual

Page 36

4–10

Chapter 4: Functional Description

Clocking and Reset Structure

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

The MAC block must run at an aggregate frequency greater than the PCS block

frequency, to support the overhead of striping and destriping.

PCS Clock Frequencies

The lane rate determines the operating frequency of the TX and RX PCS blocks. For all

variations except the 10.3125-Gbps variation, the PCS frequency is lane rate divided

by 20. For the 10.3125-Gbps variation, because the transceiver datapath width is 40

rather than 20, the PCS frequency is lane rate divided by 40. The PCS clocks are

tx_coreclkout

and rx_coreclkout.

For all variations except the 8-lane, 3.125-Gbps variation, Altera recommends that you

drive the MAC clocks at the same frequency as the PCS clock. In the 8-lane,

3.125-Gbps variation, the recommended MAC frequency is faster than the PCS

frequency.

Transceiver Reference Clock Recommended Frequency and Source

The transceiver reference clock, ref_clk, is the incoming reference clock for the

Stratix IV GX transceiver’s PLL. To achieve the recommended PCS block operating

frequency, ref_clk must have the following recommended frequency:

■

For all variations except the 10.3125-Gbps variation, the recommended ref_clk

frequency is lane rate divided by 20.

■

For the 10.3125-Gbps variation, the recommended ref_clk frequency is

322.265625 MHz, to achieve the correct lane rate of 10.3125 Gbps.

The ref_clk source affects the jitter performance of the system. For high data rate

applications, your system may require that ref_clk be generated by a GPLL on the

device.

f

For more information about driving the transceiver reference clock, refer to

10

—

312.50

318.75

—

12

—

312.50

318.75

257.81

20

—

312.50

318.75

—

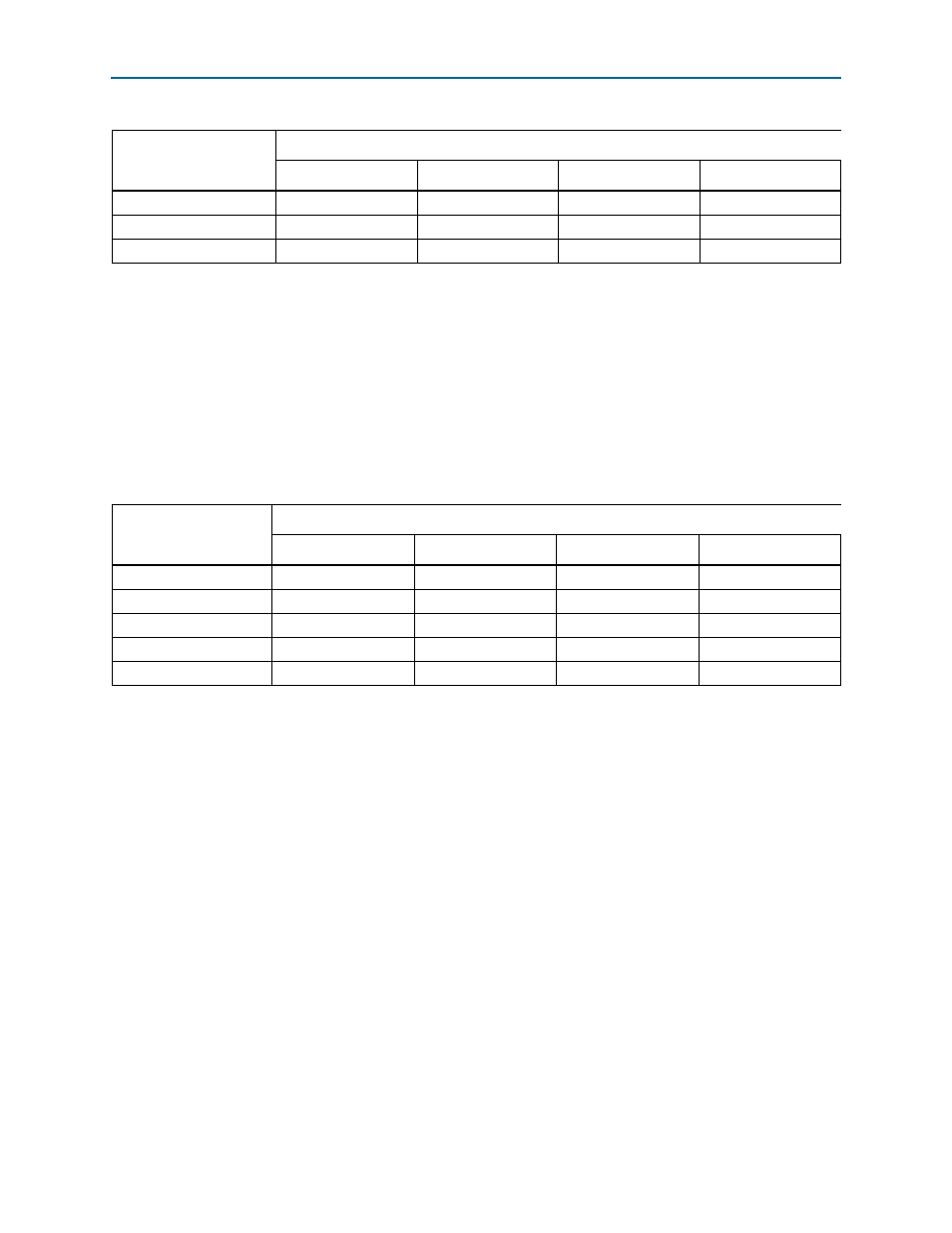

Table 4–3. Verified MAC Block Frequencies in MHz (Part 2 of 2)

Number of Lanes

Lane Rate (Gbps)

3.125

6.25

6.375

10.3125

Table 4–4. MegaCore Function PCS Block Frequencies in MHz

Number of Lanes

Lane Rate (Gbps)

3.125

6.25

6.375

10.3125

4

156.25

312.50

318.75

—

8

156.25

312.50

318.75

—

10

—

312.50

318.75

—

12

—

312.50

318.75

257.81

20

—

312.50

318.75

—