Tx application interface signals, Tx application interface signals –6, Tx application interface – Altera Interlaken MegaCore Function User Manual

Page 58

5–6

Chapter 5: Signals

Application Interface Signals

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

TX Application Interface Signals

The TX application interface provides two channels through which the application

sends data to the Interlaken link.

describe the TX application interface signals. For more

information about these signals, refer to

rx_chX_dataout_empty[T:0]

Output

Indicates the number of invalid bytes on the rx_chX_dataout_data

bus in the current rx_mac_c_clk cycle, starting from the least

significant byte. The value 1 indicates that bits [7:0] are invalid; the value

2 indicates bits [15:0] are invalid, and so on. Width is 4 bits for

variations with a 128-bit wide channel (20G/4L license), 5 bits for

variations with a 256-bit wide channel (40G/8L license), and 6 bits for

variations with a 512-bit wide channel (either of the 100G licenses). For

details, refer to

. (T = width – 1).

rx_status_calendar[P:0]

Output

RX calendar bits from the recent incoming Interlaken link control

word(s). Each 16-bit calendar page is transferred from the upstream

Interlaken partner in bits [55:40] of a single control word. The width of

the rx_status_calendar signal is 16 × the number of calendar pages

you specified in the Interlaken parameter editor. (width is 16, 128, or 256

bits; P = width – 1).

This signal is present only if you expose the calendar pages in the

Interlaken parameter editor. Refer to

“In-Band Flow Control Parameters”

“Calendar and Status Block” on page 4–20

Note to

(1) The Interlaken MegaCore function supports two channels on the application interface. The string “chX” in a signal name indicates two distinct

signal names, one with “ch0” and one with “ch1”, corresponding to the two channels, channel 0 and channel 1.

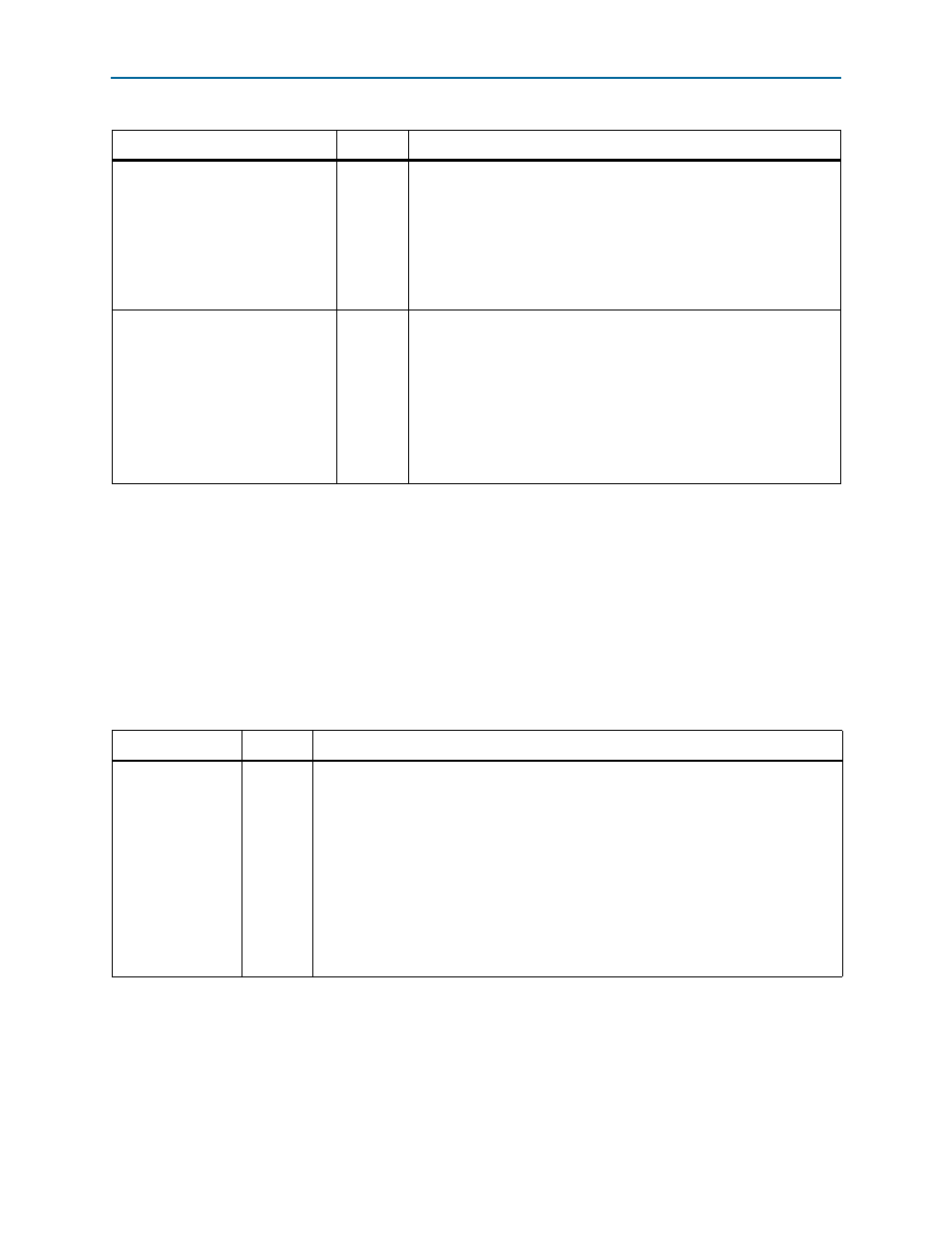

Table 5–6. RX Application Data Interface Signals

(1)

(Part 2 of 2)

Signal

Direction

Description

Table 5–7. TX Application Interface Clock Signal

Signal

Direction

Description

tx_mac_c_clk

Input

Clocks the Interlaken MegaCore function MAC TX block and therefore, also, the TX

application interface.

For all MegaCore function variations except the 8-lane, 3.125-Gbps variations, Altera

recommends that you drive this signal with the tx_coreclkout signal (in variations with

transceivers), or that you drive this signal with the same clock that drives the

tx_lane_c_clk

signal (in variations without transceivers).

For the 8-lane, 3.125-Gbps variations, the tx_mac_c_clk clock should be driven by a

faster clock than the TX PCS clock. For these variations, Altera recommends that

tx_mac_c_clk

be driven by the same clock that drives the rx_mac_c_clk. For

recommended frequencies, refer to