Table 5–8 – Altera Interlaken MegaCore Function User Manual

Page 59

Chapter 5: Signals

5–7

Application Interface Signals

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

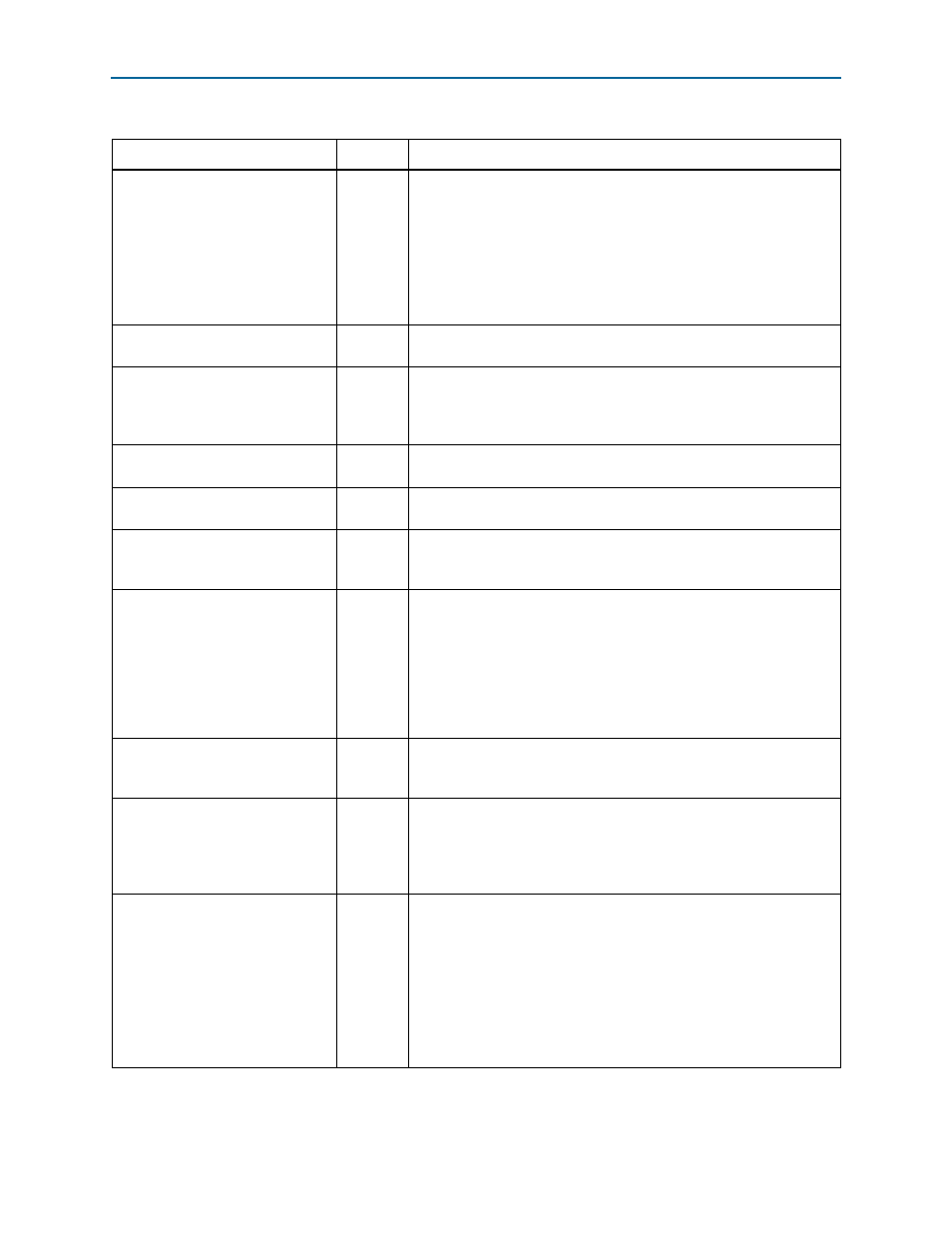

Table 5–8. TX Application Interface SIgnals

(Part 1 of 2)

Signal

Direction

Description

tx_chX_datain_data[W:0]

Input

Channel X data in. Streams in the channel X data to be transmitted on

the Interlaken interface. Width is 128 bits for variations that require the

20G/4L license, 256 bits for variations that require the 40G/8L license,

and 512 for variations that require one of the 100G licenses. For details,

refer to

The arbiter reads data from this bus when both the

tx_chX_datain_valid

and tx_chX_datain_ready signals are

asserted. For more information, refer to

.

tx_chX_datain_valid

Input

Indicates data in on the current channel (tx_chX_datain_data) is valid

in the current tx_mac_c_clk cycle.

tx_chX_datain_ready

Output

Indicates the arbiter is ready to receive data on channel X. This signal is

the Avalon-ST protocol ready output flag. The input data stream for the

current channel (tx_chX_datain_data) is backpressured until this

signal is asserted.

tx_chX_datain_startofpacket

Input

Indicates data in on the current channel in the current tx_mac_c_clk

cycle includes a start-of-packet symbol.

tx_chX_datain_endofpacket

Input

Indicates data in on current channel in the current tx_mac_c_clk cycle

includes an end-of-packet symbol.

tx_chX_datain_error

Input

Indicates an error occurred during transmission of the current packet on

tx_chX_datain_data

. This signal is valid only in an end-of-packet

cycle.

tx_chX_datain_empty[T:0]

Input

Indicates the number of invalid bytes on the tx_chX_datain_data bus

in the current tx_mac_c_clk cycle, starting from the least significant

byte. The value 1 indicates that bits [7:0] are invalid; the value 2

indicates bits [15:0] are invalid, and so on. Width is 4 bits for variations

with a 128-bit wide channel (20G/4L license), 5 bits for variations with a

256-bit wide channel (40G/8L license), and 6 bits for variations with a

512-bit wide channel (either of the 100G licenses). For details, refer to

. (T = width – 1).

tx_control_force_transmit

Input

RX calendar override. If this signal is asserted, the MegaCore function

accepts data on tx_chX_datain_data (for every enabled channel)

irrespective of the (in-band) RX calendar values.

tx_control_channel_enable

[1:0]

Input

Channel enable vector. If the bit that corresponds to channel X (bit 0 for

channel 0 and bit 1 for channel 1) is deasserted, the arbiter prevents the

transfer of data on the corresponding channel, by not asserting the

tx_chX_datain_ready

signal for that channel in response to its

tx_chX_datain_valid

signal.

tx_control_tx_calendar[P:0]

Input

TX calendar bits to send in the next outgoing Interlaken link control

word(s). Each 16-bit calendar page is transferred to the downstream

Interlaken partner in bits [55:40] of a single control word. The width of

the tx_control_tx_calendar signal is 16 × the number of calendar

pages you specified in the Interlaken parameter editor. (width is 16, 128,

or 256 bits; P = width – 1).

This signal is present only if you expose the calendar pages in the

Interlaken parameter editor. Refer to

“In-Band Flow Control Parameters”