Altera Interlaken MegaCore Function User Manual

Page 33

Chapter 4: Functional Description

4–7

Clocking and Reset Structure

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

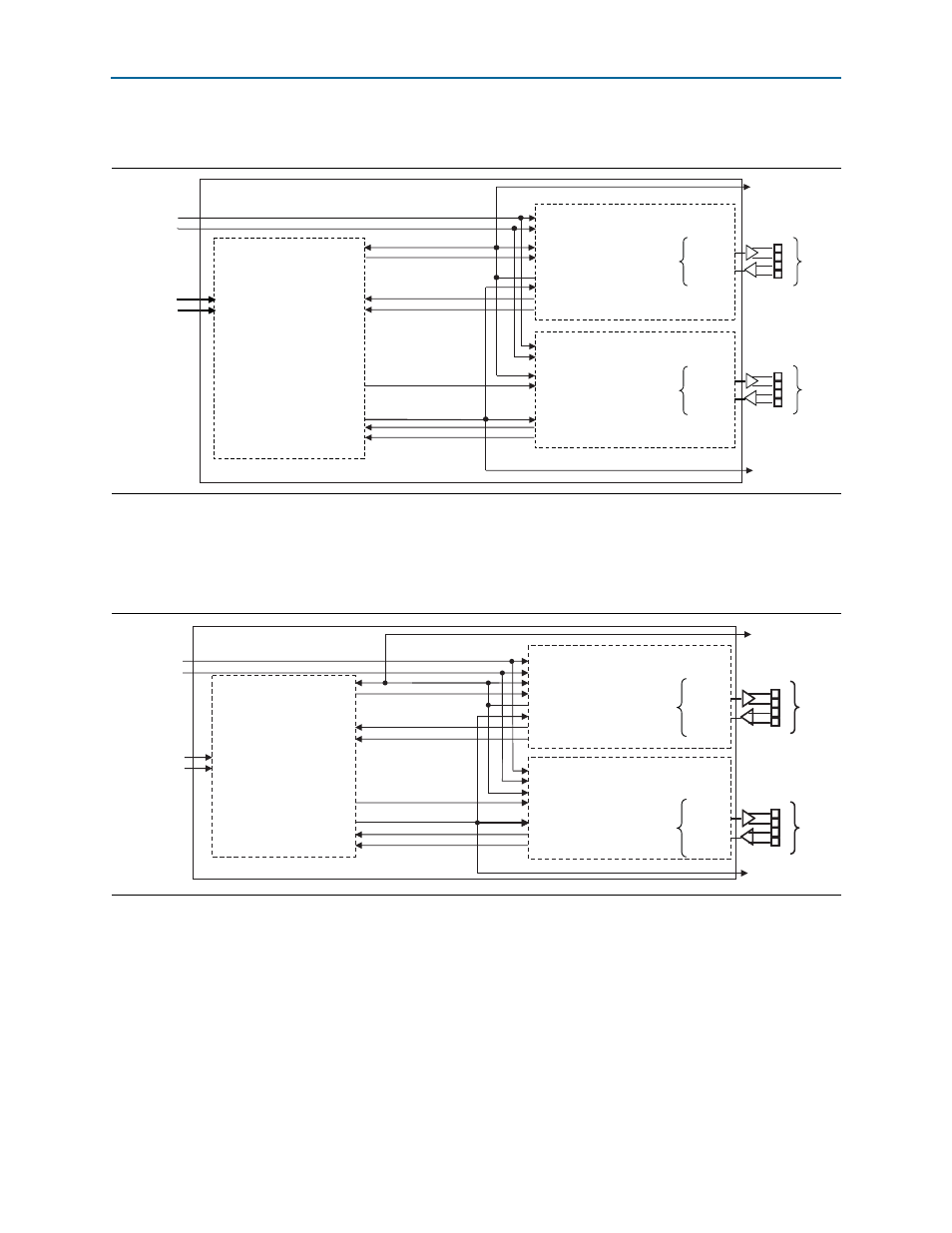

shows the clock diagram for an eight-lane Interlaken MegaCore function.

shows the clock diagram for a 10-lane Interlaken MegaCore function. This

variation uses the transceivers in PMA Direct mode. For more information, refer to

“High-Speed I/O Block” on page 4–22

.

Figure 4–3. Clock Diagram for 8-Lane Interlaken MegaCore Function

cal_blk_clk

ref_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

clk_out (master TX clock)

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

tx_lane_clk

tx_data [79:0]

tx_data [159:80]

rx_data [79:0]

rx_lane_clk [3:0]

rx_data [159:80]

rx_lane_clk [7:4]

common_rx_coreclk

HSIO Bank 0

(low latency PCS mode)

tx_coreclkout

rx_coreclkout

x4

tx_mac_clk

rx_mac_clk

tx_mac_clk

rx_mac_clk

cal_blk_clk

ref_clk

clk_in

tx_datain[79:0]

common_rx_clk

rx_dataout[79:0]

rx_clk[3:0]

tx_pin[3:0]

rx_pin[3:0]

HSIO Bank 1

(low latency PCS mode)

x4

TX MAC and PCS

RX MAC and PCS

Lanes 4 to 7

Lanes 0 to 3

Figure 4–4. Clock Diagram for 10-Lane Interlaken MegaCore Function

cal_blk_clk

ref_clk

clk_in

tx_datain[99:0]

clk_out (master TX clock)

common_rx_clk

rx_dataout[99:0]

rx_clk[4:0]

tx_lane_clk

tx_coreclkout

rx_coreclkout

tx_data[99:0]

rx_data[99:0]

rx_clk[4:0]

tx_data[199:100]

rx_data[199:100]

rx_clk[9:5]

common_rx_coreclk

HSIO Bank 0

(in PMA Direct mode)

cal_blk_clk

ref_clk

clk_in

tx_datain[99:0]

common_rx_clk

rx_dataout[99:0]

rx_clk[4:0]

HSIO Bank 1

(in PMA Direct mode)

tx_pin[4:0]

rx_pin[4:0]

tx_pin[4:0]

rx_pin[4:0]

x5

x5

tx_mac_clk

rx_mac_clk

tx_mac_c_clk

rx_mac_c_clk

cal_blk_clk

ref_clk

TX MAC

and PCS

RX MAC

and PCS

Lanes 0 to 4

Lanes 5 to 9