Calendar and status block, Calendar and status block –20, Fer to – Altera Interlaken MegaCore Function User Manual

Page 46: R to

4–20

Chapter 4: Functional Description

Calendar and Status Block

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

The packet regrouper implements an Avalon-ST interface with one important

modification: the rx_chX_dataout_empty vector can indicate the number of invalid

bytes on the rx_chX_dataout_data bus in any rx_mac_c_clk clock cycle in which it

asserts the rx_chX_dataout_valid signal, not just in clock cycles in which it asserts

rx_chX_dataout_endofpacket

. This feature supports the transmission of data to the

application interface in the arrangement that most closely reflects the format of this

data on the Interlaken link.

For more information about the RX channel interface signals, refer to

Interface Signals” on page 5–5

Calendar and Status Block

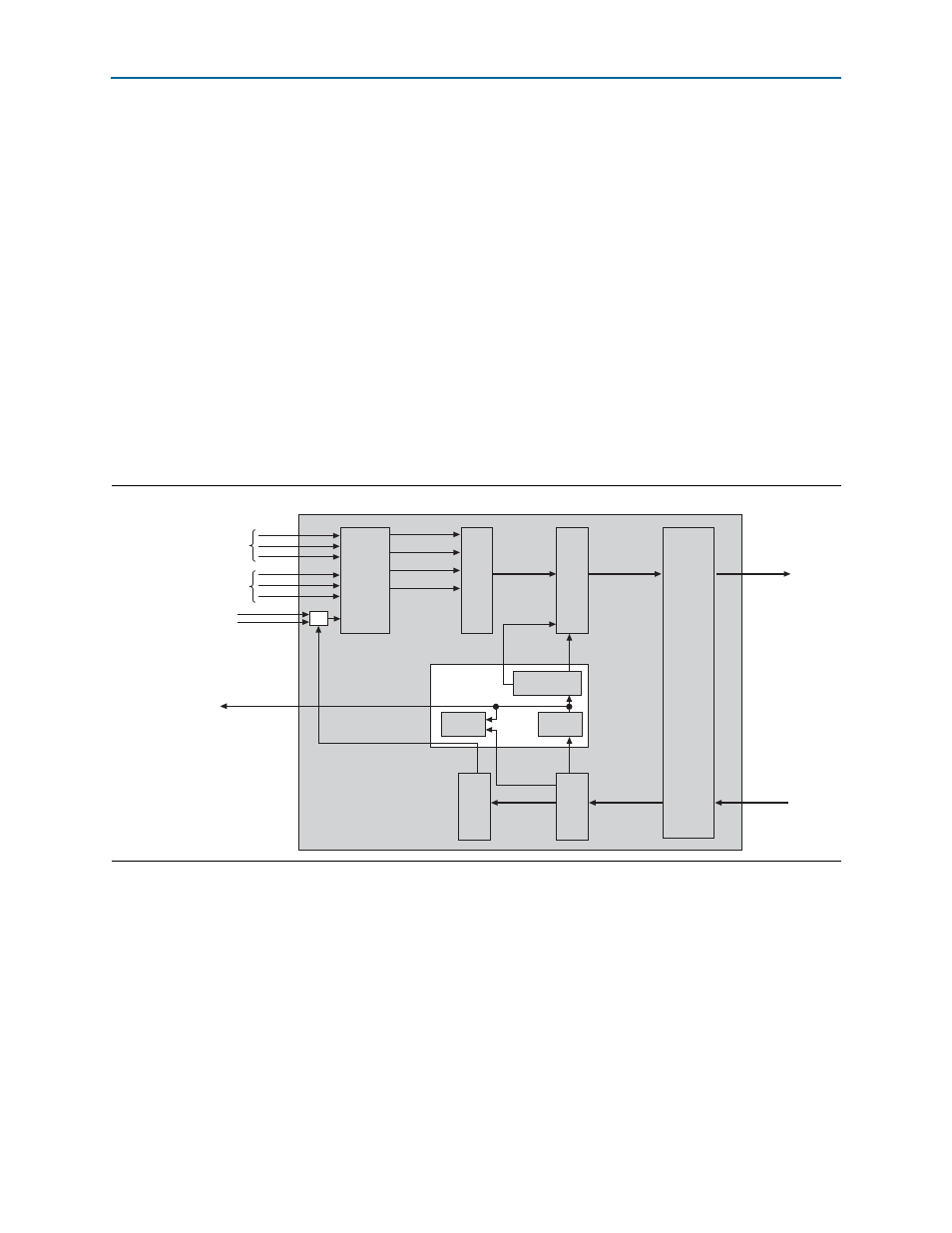

The calendar and status block collects and disseminates in-band calendar information

and lane and link status bits from the RX PCS to the TX path.

shows the calendar and status block and its sub-blocks in an Interlaken

MegaCore function with Expose calendar ports turned off.

Figure 4–15. Calendar and Status Block with Hidden Calendar Ports

Interlaken MegaCore Function

TX Calendar

Control

TX

PCS

TX

MAC

RX

PCS

RX

MAC

Lane

Status

Status

Counters

Calendar

and

Status

crc24_error

locked status

RX calendar

TX calendar

Arbiter

enable

Channel 0

Channel 1

data

sop

eop

channel

data

sop

eop

data

sop

eop

HSIO

Block