Altera SerialLite III Streaming MegaCore Function User Manual

Page 13

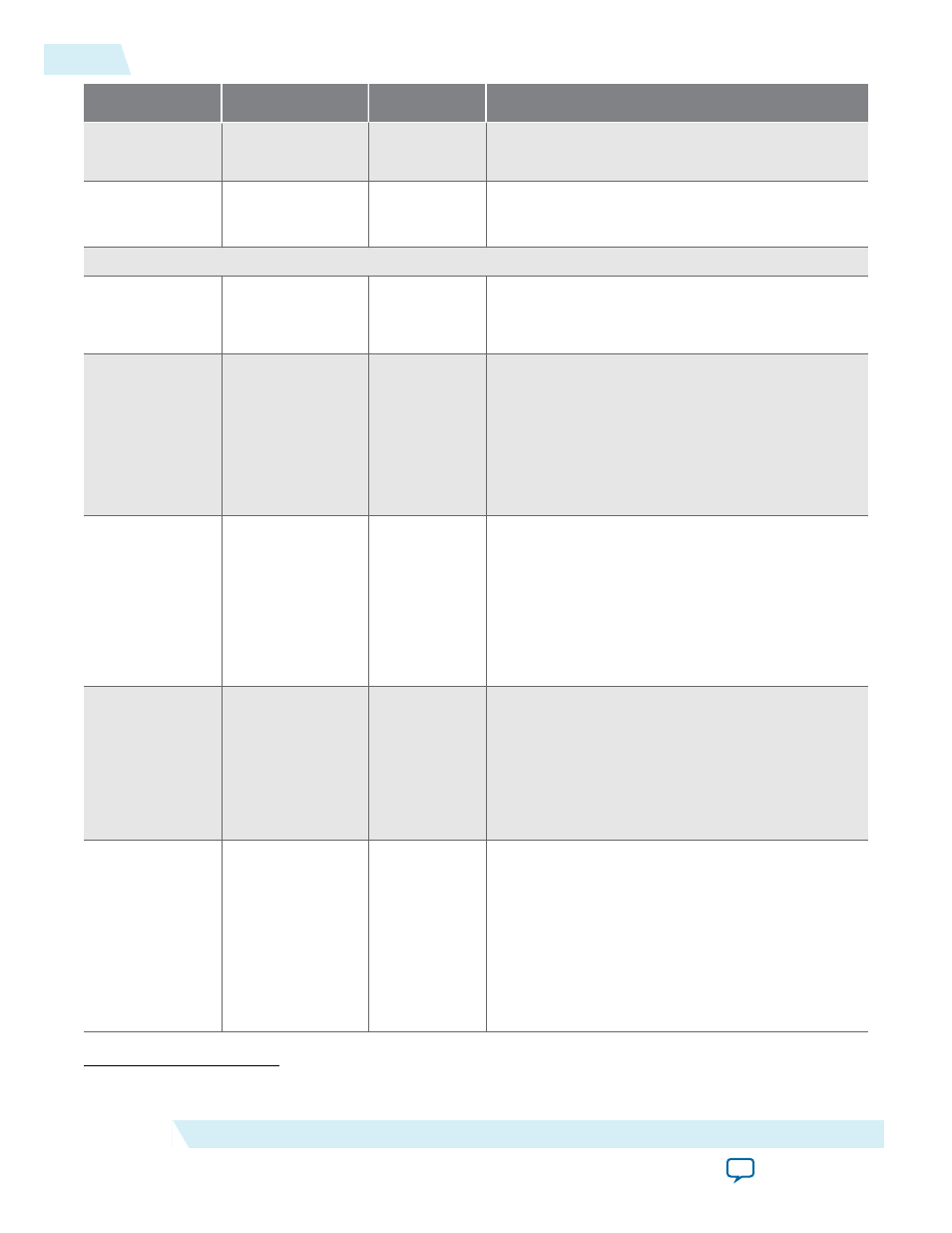

Parameter

Value

Default

Description

Meta frame

length

200–8191

8191

Specifies the metaframe length in 8-byte words.

ECC

Protection

Yes/No

No

Select to use error correcting code (ECC)

protection to strengthen the FIFO buffers from

single-event upset (SEU) changes.

Clocking and Data Rates

Advanced

clocking mode

Yes/No

No

Select to use the advanced clocking mode for your

design. The default setting is standard clocking

mode.

Required user

clock

frequency

Minimum: 50 MHz

Maximum: Limited

by the supported

transceiver data

rates

146.484375

MHz

Specifies the clock generator’s fractional PLL

(fPLL) output frequency used to drive the

user_

clock

signal. This range is device-specific and is

tied with the lane data rate and fPLL minimal

clocking constraints.

In advanced clocking mode, this signal specifies

the frequency required for the

user_clock

input.

Generated

user clock

frequency

(1)

Minimum: 50 MHz

Maximum: Limited

by the supported

transceiver data

rates

146.484375

MHz

Specifies the actual user clock frequency as

produced by the fPLL and is ideally the same as

the required clock frequency. In certain very high

precision situations where the desired user clock is

provided up to higher decimal places, this value

can vary slightly due to the fPLL constraints.

Change the required clock frequency to correct the

issue if the minute variation is intolerable.

Interface

clock

frequency

(1)

Lane rate/64

Lane rate/40

See description

205.078125

MHz

Specifies the clock frequency of the source, sink, or

duplex user interface in advanced clocking mode.

Arria 10 15.625 Gbps ≤ lane rate ≤ 17.4 Gbps:

Lane rate/64

Arria 10 < 15.625 Gbps, and all Stratix V and Arria

V GZ: Lane rate/40

Core clock

frequency

(1)

(Lane rate/64) to

(Lane rate/67)

(Lane rate/40)–to

(Lane rate/67)

See description

205.078125

MHz

The core clock is used internally between the user

domain and the Native PHY IP core (Arria 10

devices) or Interlaken PHY IP core (Stratix V and

Arria V GZ devices).

Arria 10 15.625 Gbps ≤ lane rate ≤ 17.4 Gbps:

(Lane rate/64) to (Lane rate/67)

Arria 10 < 15.625 Gbps, and all Stratix V and Arria

V GZ: (Lane rate/40) to (Lane rate/67)

(2)

(1)

The parameter editor automatically calculates this parameter value based on the general design options.

3-4

SerialLite III Streaming IP Core Parameters

UG-01126

2015.05.04

Altera Corporation

Getting Started