Clock domains, Clock domains -10 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 34

tx_serial_clk

). The Seriallite III Streaming IP core uses a transmit serial clock input

bus (

tx_serial_clk

) and

tx_pll_locked

input to connect the external transmit PLL to the Arria 10

Native PHY IP core. Refer to the Arria 10 Transceiver PHY User Guide for more information.

Related Information

•

•

For more information about the Arria 10 Native PHY IP core.

•

For more information about the Interlaken PHY IP core.

Clock Domains

The SerialLite III Streaming IP core contains different clock domains, depending on the clocking mode.

In addition to these clock domains, there are another four clock domains in isolation within the

transceivers.

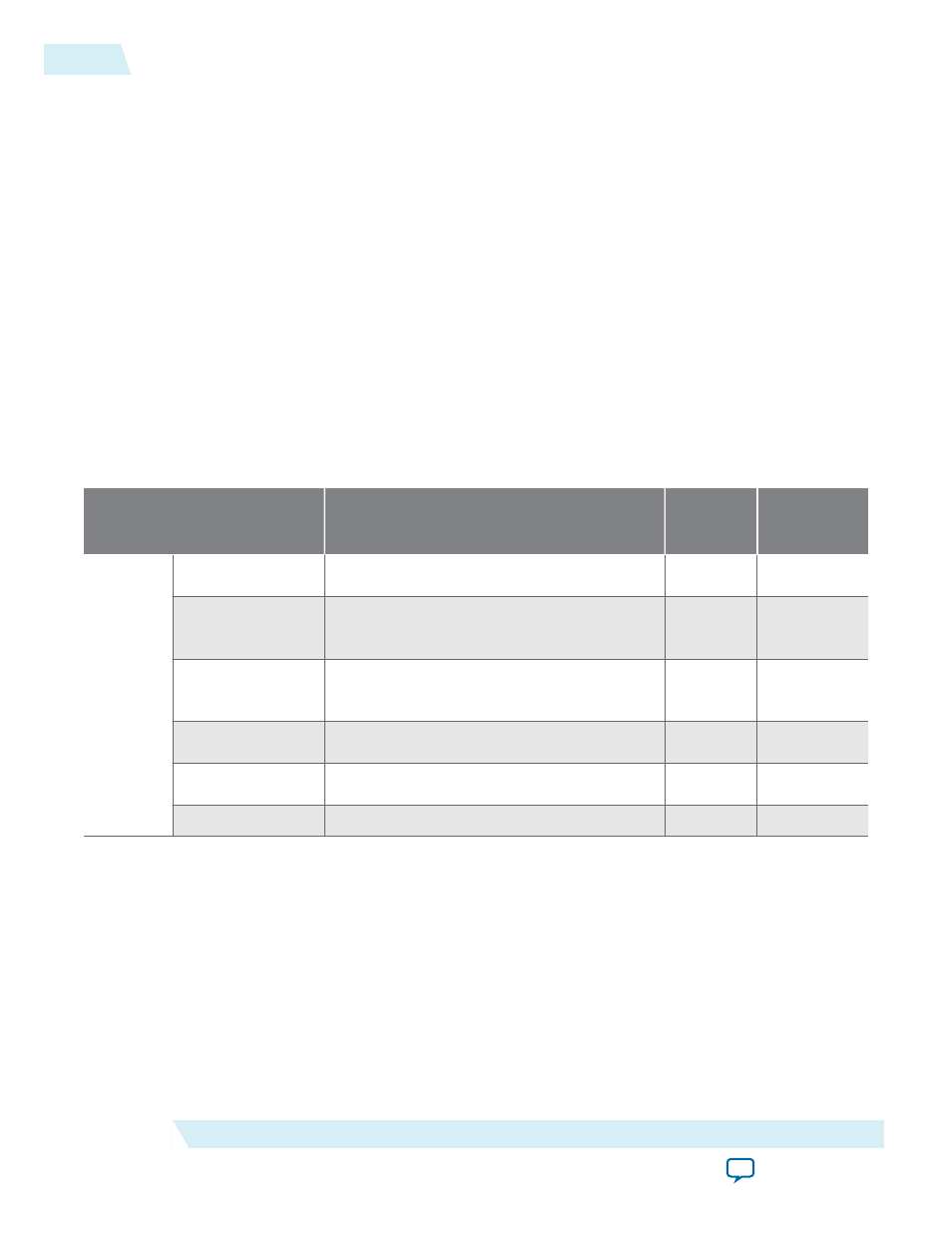

Table 4-3: SerialLite III Streaming IP Core Clock Domains and Signals

Clock Domain

Description

Standard

Clocking

Mode

Advanced

Clocking Mode

Source

Core

user_clock

Source user interface clock

Yes

Yes

phy_mgmt_clk

Source Native PHY or Interlaken PHY IP core

reconfiguration interface clock

Yes

Yes

pll_ref_clk

Source transceiver reference clock (Stratix V

and Arria V GZ only)

Yes

Yes

tx_coreclkin

Source core clock (in standard clocking mode) Yes

tx_clkout

Source core clock (in advanced clocking mode)

Yes

tx_serial_clk

Transmit transceiver clock (Arria 10 only)

Yes

Yes

4-10

Clock Domains

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Functional Description