Design example components, Seriallite iii streaming ip core, Source user clock – Altera SerialLite III Streaming MegaCore Function User Manual

Page 58: Traffic generator, Design example components -3

Related Information

•

•

Design Example Components

The design example consists of following components:

• SerialLite III Streaming IP core variation

• Source fPLL (to generate source user clock in advanced clocking mode)

• Traffic generator

• Traffic checker

• Demo control

• Demo management

SerialLite III Streaming IP Core

The SerialLite III Streaming IP core variation accepts data from the traffic generator and formats the data

for transmission. It also receives data from the link, strips the headers, and presents it to the traffic

checker for analysis. The core is generated using the parameter editor in the Quartus II software.

Source User Clock

The fPLL is available only in designs utilizing the advanced clocking mode to generate a user clock for

sourcing data into the SerialLite III Streaming IP core.

Traffic Generator

The traffic generator generates traffic in a deterministic format to verify that data is transmitted correctly

across the link. Traffic consists of sets of sample words, one for each lane on the link, that are presented to

the source user interface.

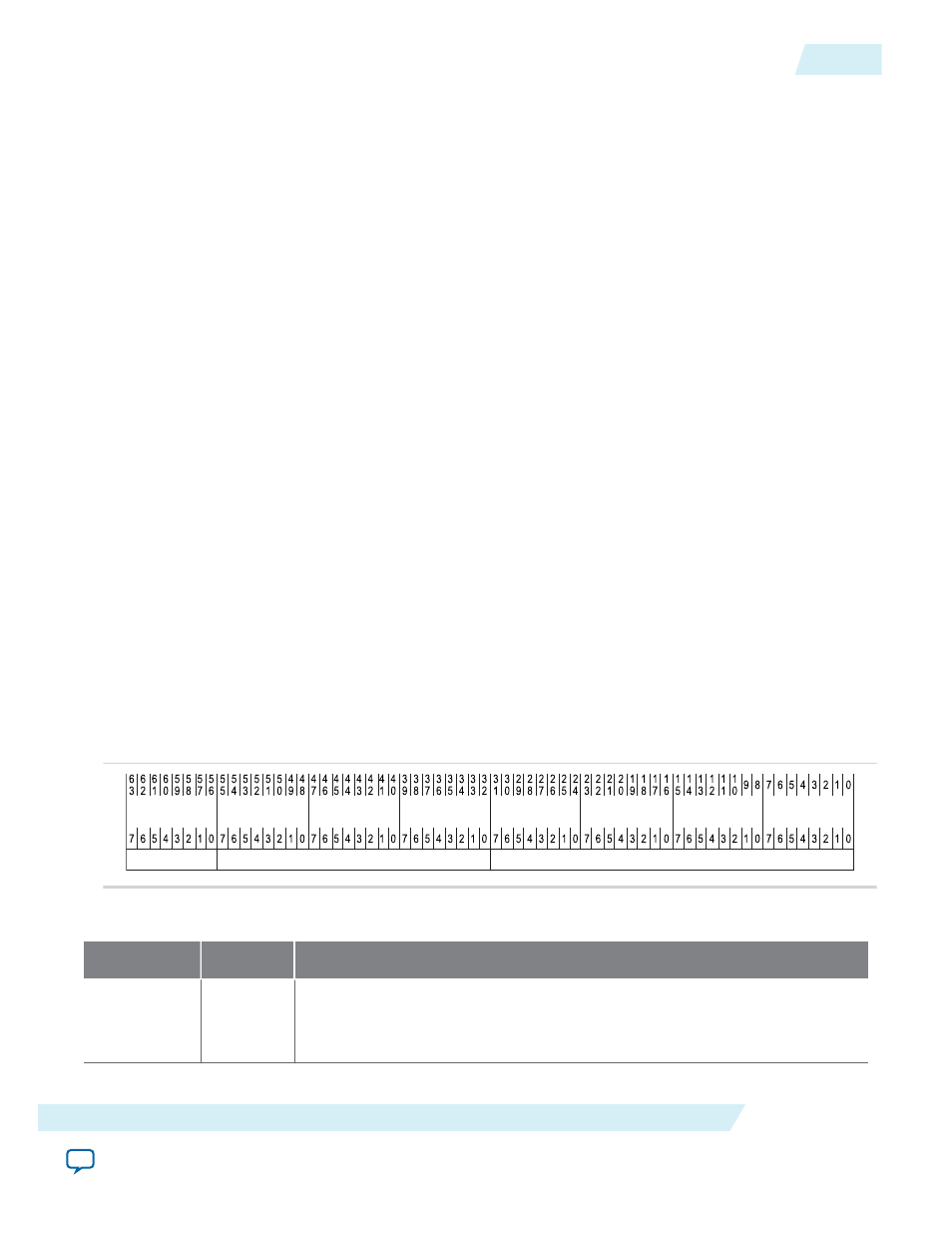

Figure 5-3: Traffic Generator Sample Word Format

This figure shows the format of the sample words generated for each lane.

Word ID

Burst Count

Word Count

Byte 7

Byte 6

Byte 5

Byte 4

Byte 3

Byte 2

Byte 1

Byte 0

Table 5-1: Traffic Generator Sample Word Fields

Field

Bits

Description

Word ID

63–59

Contains a static value to distinguish which 64-bit word on the user interface

that this sample was presented on. The Word ID value ranges from 0 to

(lanes–1).

UG-01126

2015.05.04

Design Example Components

5-3

SerialLite III Streaming IP Core Design Guidelines

Altera Corporation