Seriallite iii streaming source core, Seriallite iii streaming source core -3 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 27

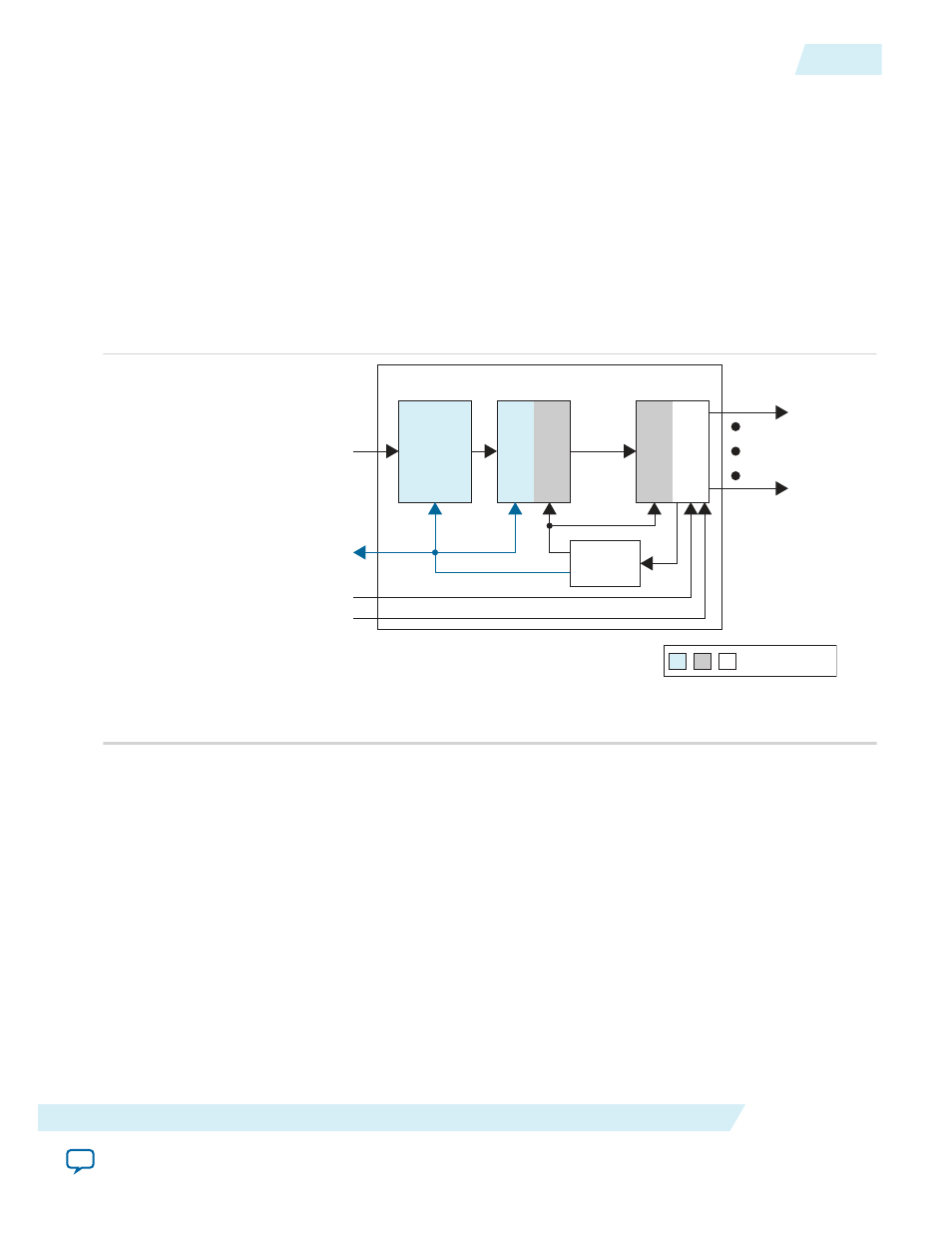

SerialLite III Streaming Source Core

The source core consists of five major functional blocks (the implementation varies depending on the

clocking mode):

• Clock generator (in the standard clocking mode)

• Source application module

• Source adaptation module

• Native PHY IP TX core - Interlaken mode (Arria 10 devices)

• Interlaken PHY IP TX core (Stratix V and Arria V GZ devices)

• PPM-Absorption module (in the advanced clocking mode only)

Figure 4-3: SerialLite III Streaming Source Core (Standard Clocking Mode)

Application

Module

SerialLite III Streaming Source

Transceiver Reconfiguration Clock

Source User Interface

SerialLite III

Streaming Link

Adaptation

Module

Clock

Generator

Source User Clock

Core Clock

Clock Domains

Transceiver Reference Clock

or Transmit Serial Clock (1)

Notes:

1. Transceiver reference clock for Stratix V and Arria V GZ devices; transmit serial clock for Arria 10 devices.

2. Native PHY IP core for Arria 10 devices and Interlaken PHY IP core for Stratix V and Arria V GZ devices.

PHY IP

Core (2)

UG-01126

2015.05.04

SerialLite III Streaming Source Core

4-3

SerialLite III Streaming IP Core Functional Description

Altera Corporation