Altera SerialLite III Streaming MegaCore Function User Manual

Page 9

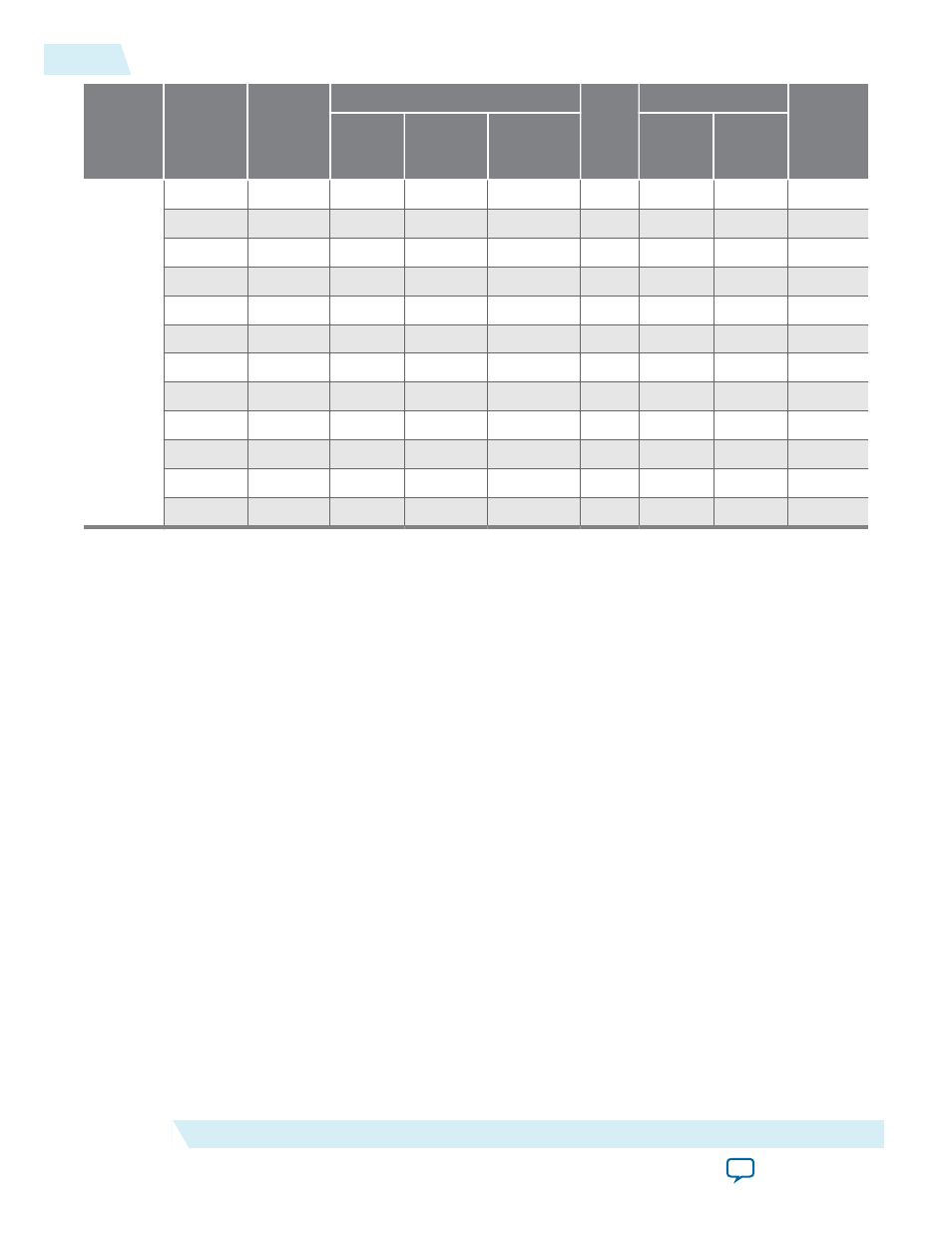

Device

Direction

Clocking

Mode

Parameters

ALMs

Logic Registers

M20K

Number

of Lanes

Per-Lane

Data Rate

(Mbps)

ECC

Primary Secondary

Stratix

V GX

and

Arria

V GZ

Source

Standard 24

10312.50 Disabled

6257

4511

142

48

Standard 24

10312.50 Enabled

7191

6636

459

72

Advanced 24

10312.50 Disabled

6265

4482

196

87

Advanced 24

10312.50 Enabled

8038

9013

761

121

Sink

Standard 24

10312.50 Disabled

5159

7962

267

48

Standard 24

10312.50 Enabled

3779

9761

802

72

Advanced 24

10312.50 Disabled

6058

7995

258

0

Advanced 24

10312.50 Enabled

5891

9789

905

72

Duplex

Standard 24

10312.50 Disabled

4680

11819

482

96

Standard 24

10312.50 Enabled

6419

15829

1249

144

Advanced 24

10312.50 Disabled

5582

11779

514

87

Advanced 24

10312.50 Enabled

7018

18393

1410

193

Related Information

More information about Quartus II resource utilization reporting.

2-4

Performance and Resource Utilization

UG-01126

2015.05.04

Altera Corporation

About the SerialLite III Streaming IP Core