Sink core link debugging, Sink core link debugging -9, Figure 5-5: sink core link debugging flow chart – Altera SerialLite III Streaming MegaCore Function User Manual

Page 64: Table 5-3: sink link debug signals

Sink Core Link Debugging

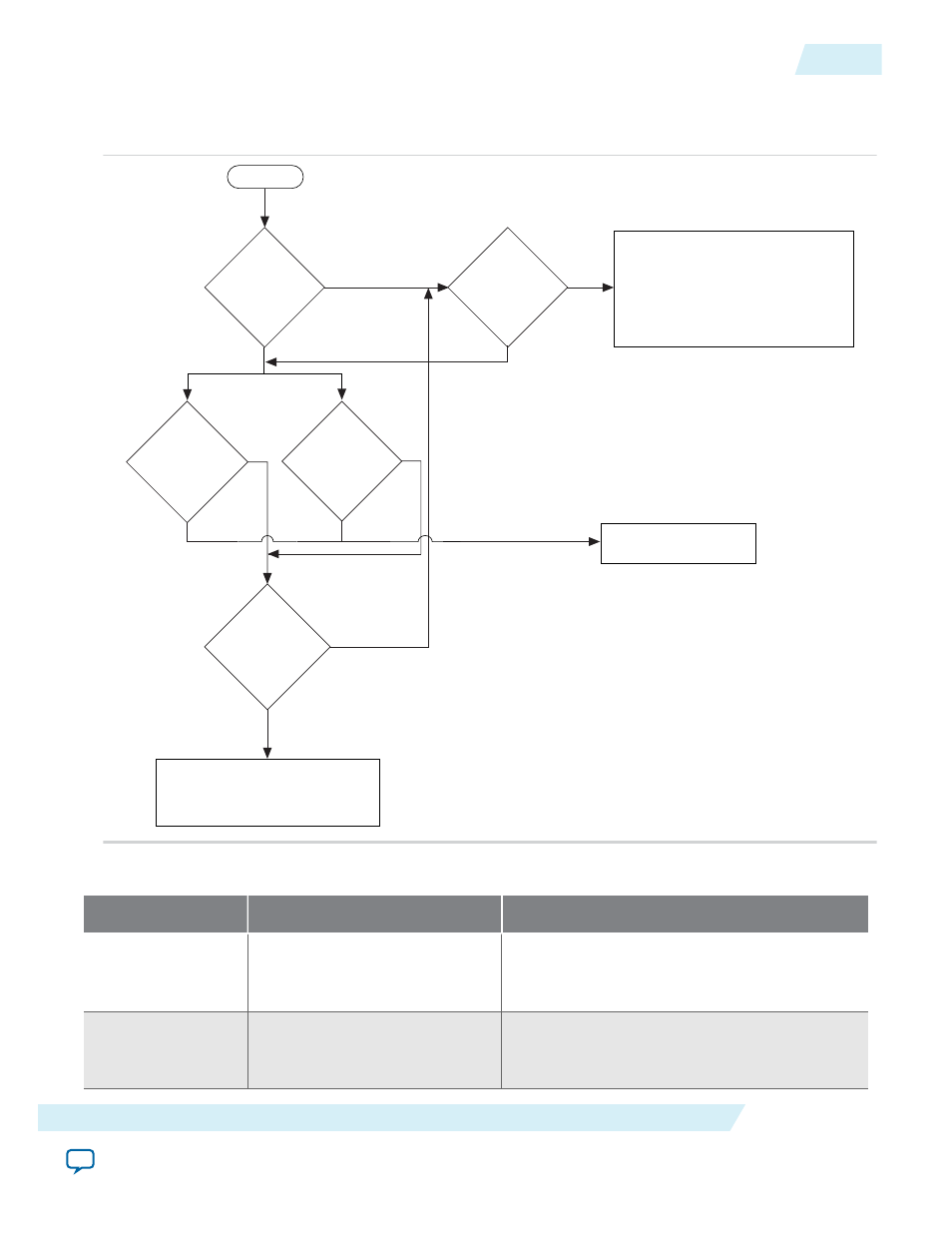

Figure 5-5: Sink Core Link Debugging Flow Chart

Sink Link

rx_aligned

properly asserted?

(Indicating that the

lanes are properly

aligned)

yes

no

Are there

any CRC-32

errors?

yes

no

rx_frame_lock

asserted for all

the lanes?

yes

no

Deasserted/Toggling

rx_ready_stable?

(Indicating transceivers

are properly reset)

no

rx_is_lockedtodata

asserted for all

the lanes?

yes

no

Signal Integrity Issues:

- Check the transceiver analog parameters.

- Manually visualize and open up the link eye

- Refer to the Altera Transceiver PHY IP User Guide on

how to measure and set the transceiver analog parameters.

- The Transceiver Toolkit provides a reference design that can

be used to sweep for proper transceiver analog settings.

yes

- Check the transceiver reference clock

- Check the cables

- Verify that the reconfiguration controller (RC)

is properly hooked up.

- Make sure that the latencies of the reset going into the

RC and into the cores (phy_mgmt_clk_reset) are equal.

Table 5-3: Sink Link Debug Signals

Signal Name

Location

Description

rx_aligned

/sink/rx_aligned

This active high signal indicates that the lanes

are properly aligned. This signal should remain

asserted for proper operation.

rx_ready

/sink/rx_ready

An asserted value for this active high signal

indicates that the reset sequence for the sink

PCS is complete.

UG-01126

2015.05.04

Sink Core Link Debugging

5-9

SerialLite III Streaming IP Core Design Guidelines

Altera Corporation