Altera SerialLite III Streaming MegaCore Function User Manual

Page 54

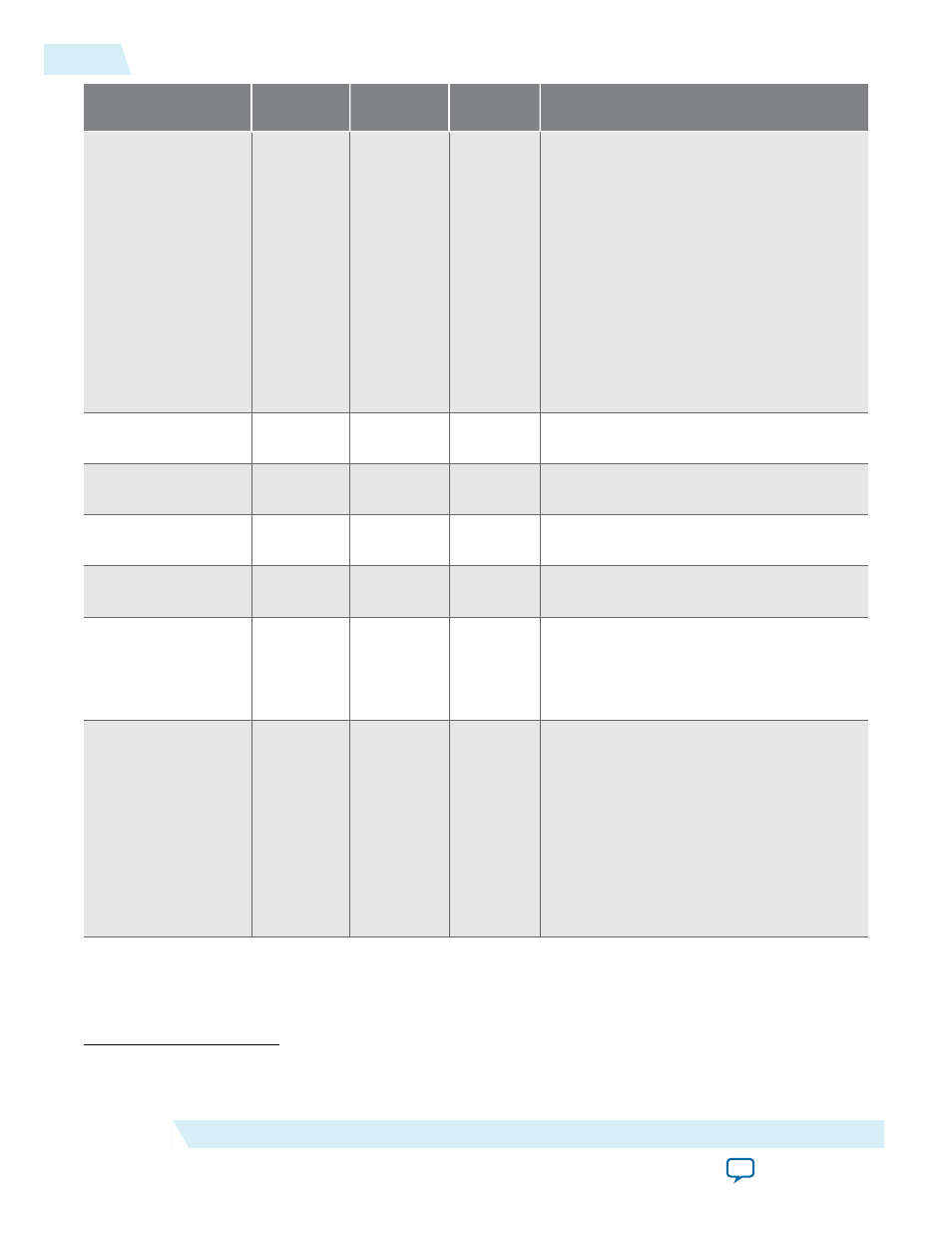

Signal

Width

Clock

Domain

Direction

Description

phy_mgmt_addr[N:

0]

9 (Stratix V

and Arria V

GZ)

11 - 16

(Arria 10)

phy_mgmt_

clk

Input

Control and status register (CSR) address

for Arria 10 devices.

The width depends on the number of

lanes. The parameter editor determines

the required width for you.

You have to manually tie this extra bit

(4)

:

• phy_mgmt_addr[msb] = 1: for

Transceiver reconfiguration usage.

• phy_mgmt_addr[msb] = 0: for soft

CSR (the transceiver reset and

loopback control CSR)

phy_mgmt_

writedata[31:0]

32

phy_mgmt_

clk

Input

CSR write data.

phy_mgmt_

readdata[31:0]

32

phy_mgmt_

clk

Output

CSR read data.

phy_mgmt_write

1

phy_mgmt_

clk

Input

Active high CSR write signal.

phy_mgmt_read

1

phy_mgmt_

clk

Input

Active high CSR read signal.

phy_mgmt_

waitrequest

1

phy_mgmt_

clk

Output

CSR read or write request signal. When

asserted, this signal indicates that the

Avalon-MM slave interface is unable to

respond to a read or write request.

reconfig_busy

1

phy_mgmt_

clk

Input

For Stratix V and Arria V GZ devices,

when asserted, this signal indicates that a

reconfiguration operation is in progress

and no further reconfiguration operations

should be performed. You can monitor

this signal to determine the status of the

Transceiver Reconfiguration Controller.

For Arria 10 devices, this signal is present

but unused; tie this signal to 1’b0.

(4)

For more information about this bit, refer to the Interlaken PHY Registers table in the Altera Transceiver

PHY IP Core User Guide.

4-30

Signals

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Functional Description