Altera SerialLite III Streaming MegaCore Function User Manual

Page 23

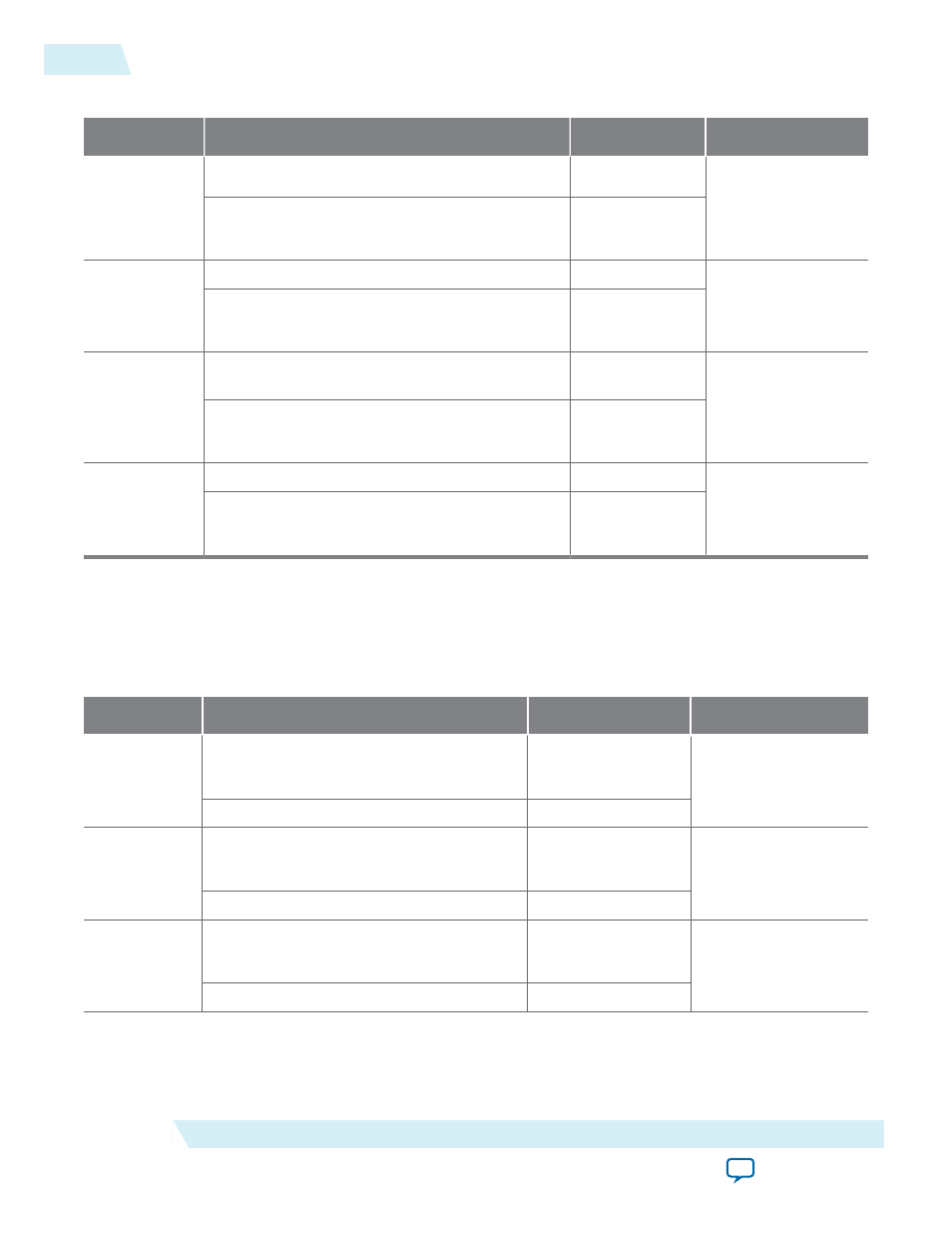

Table 3-4: Testbench Simulation Scripts

Simulator

File Directory

Device Family

Script

ModelSim-

Altera SE/

AE

<example design name>/example_testbench/vsim/ Arria 10

vsim -c -do

run_vsim.do

<variation name>_example/seriallite_iii_sv/

example_testbench/vsim/

Stratix V

Arria V GZ

VCS/VCS

MX

<example design name>/example_testbench/vcs/

Arria 10

run_vcs.sh

<variation name>_example/seriallite_iii_sv/

example_testbench/vcs/

Stratix V

Arria V GZ

NCSim

<example design name>/example_testbench/

ncsim/

Arria 10

run_ncsim.sh

<variation name>_example/seriallite_iii_sv/

example_testbench/ncsim/

Stratix V

Arria V GZ

Aldec

Riviera

<example design name>/example_testbench/aldec/ Arria 10

run_aldec.sh

<variation name>_example/seriallite_iii_sv/

example_testbench/aldec/

Stratix V

Arria V GZ

By default, the parameter editor generates simulator-specific scripts containing commands to compile,

elaborate, and simulate Altera IP models and simulation model library files. You can copy the commands

into your simulation testbench script, or edit these files to add commands for compiling, elaborating, and

simulating your design and testbench.

Table 3-5: Altera IP Core Simulation Scripts

Simulator

File Directory

Device Family

Script

ModelSim-

Altera SE/

AE

<variation name>_sim/mentor

Stratix V

Arria V GZ

msim_setup.tcl

<variation name>/sim/mentor

Arria 10

VCS

<variation name>_sim/synopsys/vcs

Stratix V

Arria V GZ

vcs_setup.sh

<variation name>/sim/synopsys/vcs

Arria 10

VCS MX

<variation name>_sim/synopsys/vcsmx

Stratix V

Arria V GZ

vcsmx_setup.sh

synopsys_sim.setup

<variation name>/sim/synopsys/vcsmx

Arria 10

3-14

Simulating and Verifying the Design

UG-01126

2015.05.04

Altera Corporation

Getting Started