Traffic checker, Demo control, Demo management – Altera SerialLite III Streaming MegaCore Function User Manual

Page 59: Nios ii processor code, Design setup, Design setup -4

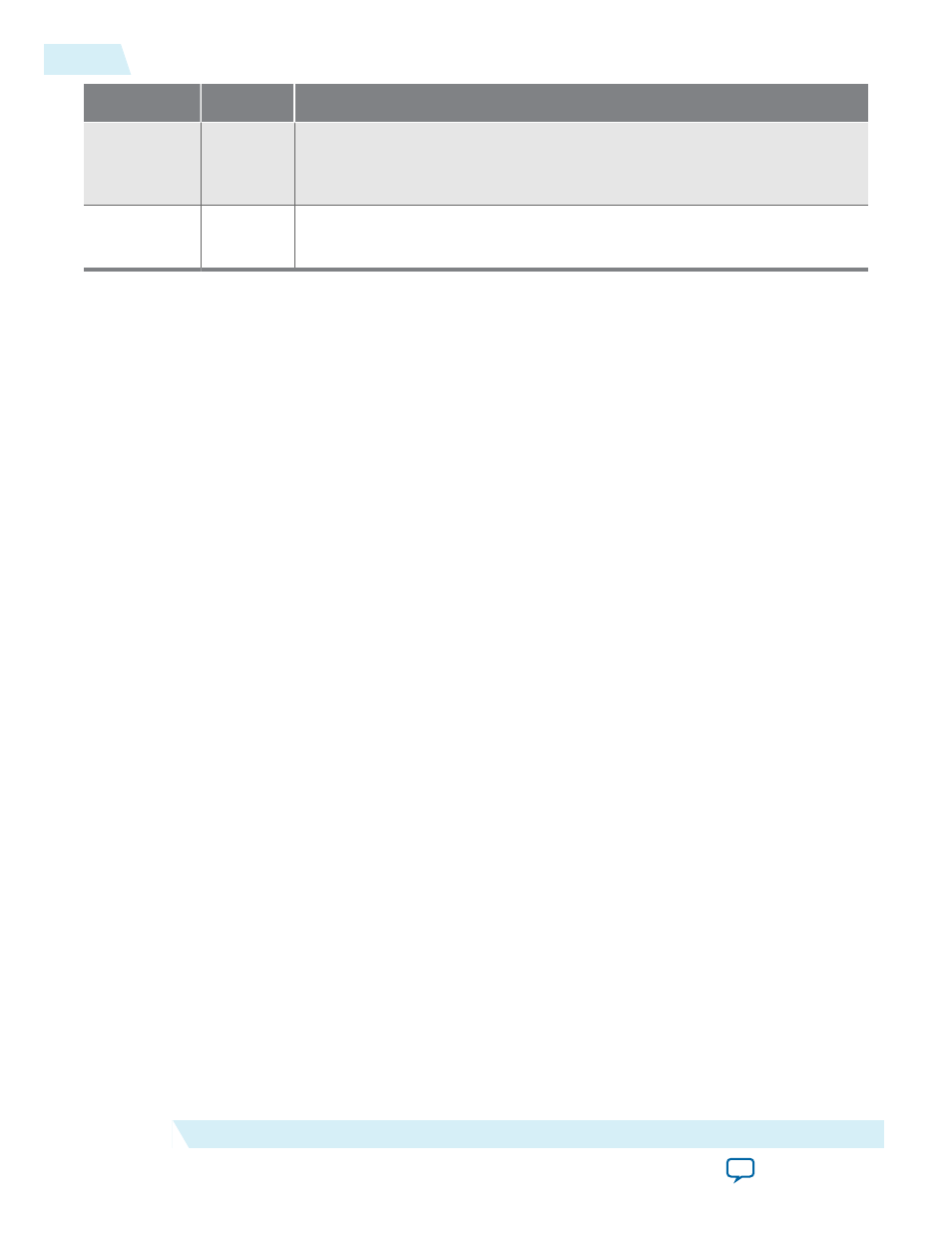

Field

Bits

Description

Burst

Count

58–32

Tracks the number of bursts used to transfer the sample data. This field value

starts with one after reset and is incremented each time the

start_of_burst

signal is asserted on the source user interface.

Word

Count

31–0

Tracks the number of valid sample words that have been transferred, across all

bursts, to the source user interface.

Traffic Checker

The traffic checker performs the following inspections to verify that the received data conforms to the

expected format:

• Checks each sample word to verify that the expected word ID was received.

• Checks each sample word to verify that the word count value is higher than the word count value from

the last valid sample word.

• Verifies that lane de-skew has been properly performed by validating that the word count and burst

count values from the sample word are the same as the values received from the adjacent lane.

• If the

start_of_burst

signal is asserted on the user interface, verifies that the burst count value in the

current sample word is higher than the burst count value from the last valid sample word. Otherwise, it

verifies that the burst count value has not changed.

Demo Control

The demo control module is a Nios

®

II processor system, generated in Qsys, to control the demo

hardware. In addition to the Nios II processor system, this module also includes reconfiguration control‐

lers for the transceivers and PLL channels in the SerialLite III Streaming IP core. The number of reconfi‐

guration interfaces equal to the number of transceivers plus PLL channels for the source and duplex cores,

and the number of transceivers for the sink cores.

Demo Management

The demo management module implements CSRs to control and monitor the design operation. This

includes CSRs to monitor and log errors that occur during the operation.

Nios II Processor Code

The Nios II processor controls the options exercised in the design example. The code also enables CRAM

bits for CRC-32 error injection support. The error injection support in 10G PCS is based on groups of

three channels or triplets. Setting the corresponding bit for a given channel in the triplet enables CRC

error injection for all of the lanes that use any channel in the given triplet.

The design example sets the bit for channel 0 that is connected to lane 0 in the example design. Therefore,

CRC error injection is exercisable for lane 0 only. Refer to the Nios II processor source code

(demo_control.c) for information on setting bits for other channels.

Design Setup

The design example targets the Transceiver Signal Integrity Development Kit, Stratix V GT Edition. The

design includes an SDC script as well as a QSF with verified constraints and settings for a 2-lane design in

5-4

Traffic Checker

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Design Guidelines