Source clock generator – Altera SerialLite III Streaming MegaCore Function User Manual

Page 28

Figure 4-4: SerialLite III Streaming Source Core (Advanced Clocking Mode)

Application

Module

PHY IP

Core (1)

SerialLite III Streaming Source

Transceiver Reconfiguration Clock

Source User Interface

SerialLite III

Streaming Link

Adaptation

Module

Transceiver Reference Clock

Core Clock

PPM

Absorber

Module

User Interface Clock

Clock Domains

Note:

1. Native PHY IP core for Arria 10 devices and Interlaken PHY IP core for Stratix V and Arria V GZ devices.

on page 4-6

Source Clock Generator

The clock generator in the source core synthesizes the user clock (

user_clock

) and core clock signals

(

tx_coreclockin

) from the Native PHY IP core (Arria 10 devices) or Interlaken PHY IP (Stratix V and

Arria V GZ devices) core's output clock signal (

tx_clkout

). This clock generator consists of a fractional

PLL and a state machine responsible for clocks generation and reset sequencing. The

user_clock_reset

is not released until the fPLL is locked. The module is used in the standard clocking mode only.

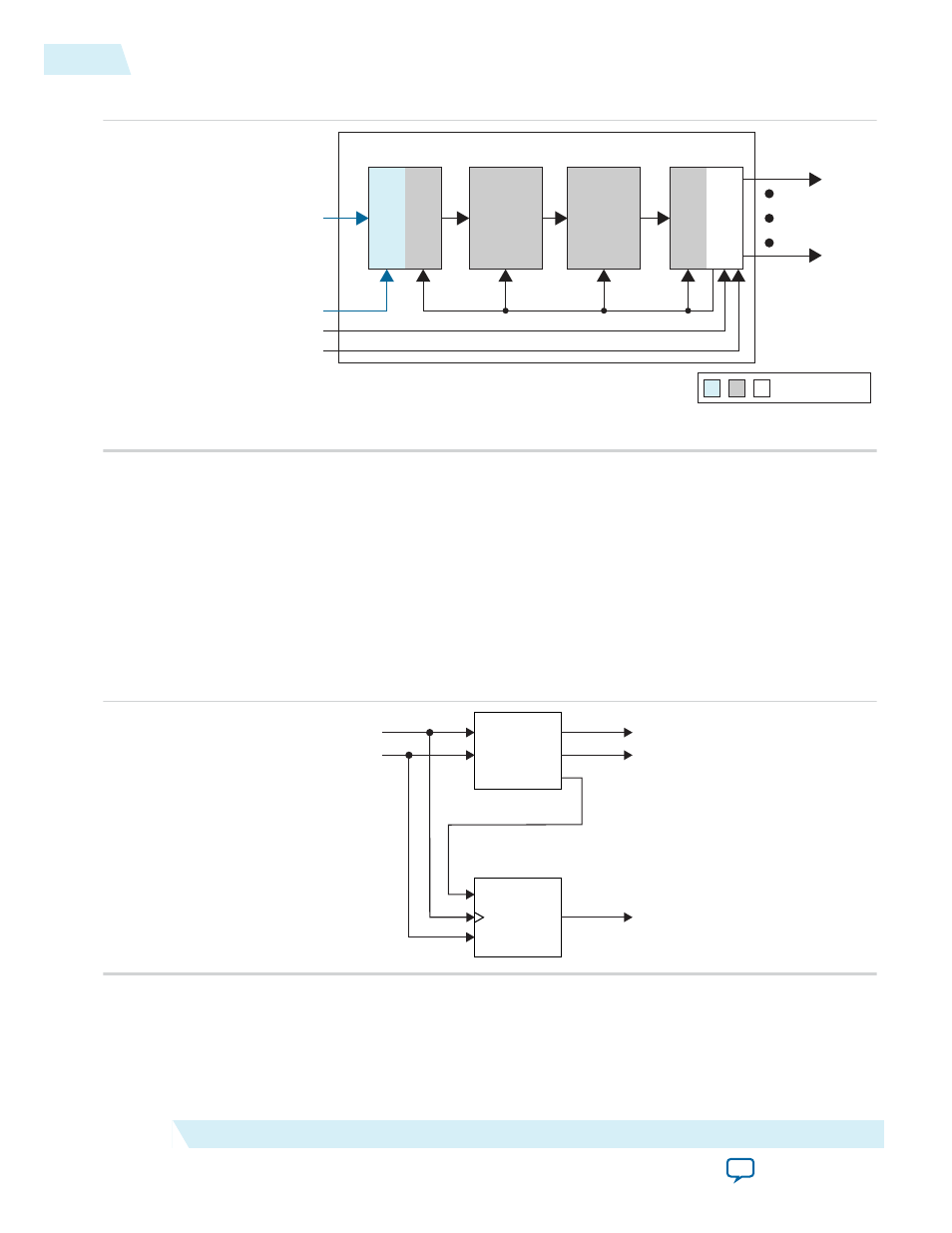

Figure 4-5: Clock Generator Block Diagram

Reset

State

Machine

Fractional

PLL

phy_mgmt_clk_reset

tx_coreclkin

user_clock

lock

user_clock_reset

tx_clkout

• For lane rates < 15.625 Gbps and all Stratix V and Arria V GZ devices, the fPLL generates the

user_clock/user_clock_tx

and

tx_coreclkin

based on fixed ratios determined by the SerialLite III

Streaming parameter editor.

4-4

Source Clock Generator

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Functional Description