Altera SerialLite III Streaming MegaCore Function User Manual

Page 14

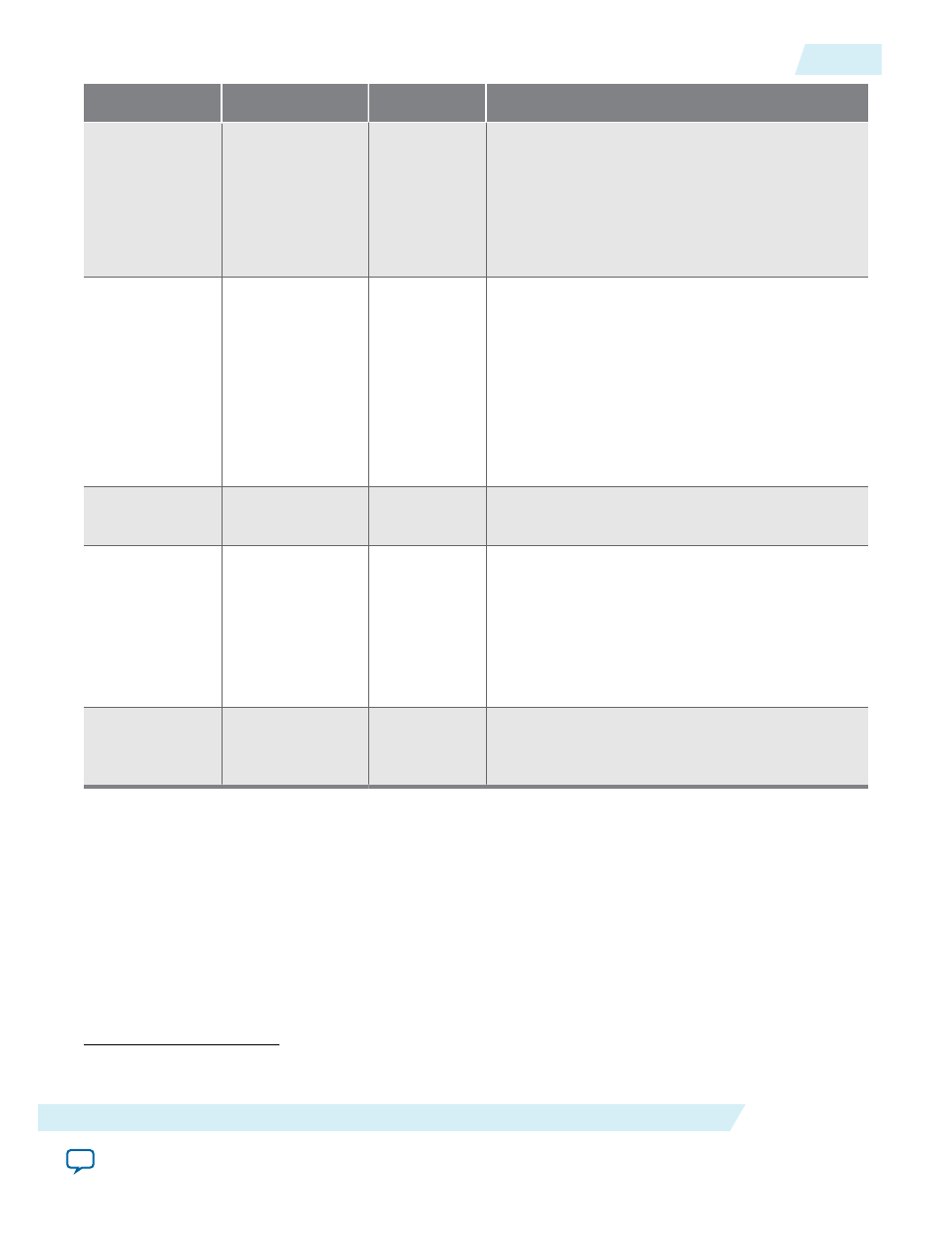

Parameter

Value

Default

Description

fPLL

reference

clock

frequency

(1)

Lane rate/64

Lane rate/40

See description

257.812500

MHz

Specifies the fPLL reference clock frequency in

standard clocking mode.

Arria 10 15.625 Gbps ≤ lane rate ≤ 17.4 Gbps: lane

rate/64

Arria 10 < 15.625 Gbps, and all Stratix V and Arria

V GZ: Lane rate/40

(2)

Transceiver

reference

clock

frequency

Range supported

by the transceiver

PLLs (Lane rate/N)

644.53125

MHz

Specifies the transceiver reference clock frequency.

The default value for the Input clock frequency is

lane rate/16. Sample values of N include 80, 64, 50,

40, 32, 25, 20, 16, 12.5, 10, and 8.

Altera recommends that you select the highest

frequency among the available options in the

drop-down list.

For Arria 10 source designs, set this parameter to

none.

Input data

rate per lane

(1)

64 × (User clock

frequency)

9.375 Gbps

Input data rate that the core can support.

Transceiver

data rate per

lane

(1)

Input data rate ×

Overheads

10.3125 Gbps

The effective data rate at the output of the

transceivers, incorporating transmission and other

overheads.

The parameter editor automatically calculates this

value by adding the input data rate with transmis‐

sion overheads to provide you with a selection of

user clock frequency.

(2)

Aggregate

input data

rate

(1)

Lanes × Input data

rate

36.6210938

Gbps

Aggregate input data rate that the core can

support.

Related Information

SerialLite III Parameter Editor

on page 3-2

Transceiver Reconfiguration Controller for Stratix V and Arria V GZ

Designs

If your design targets Stratix V or Arria V GZ devices, the transceiver reconfiguration controller is not

included in the generated IP core. To create a complete system, refer to the design example block diagram

on how to connect the transceiver reconfiguration controller.

(2)

The clock frequency value is useful if you want to simulate designs at different data rates. You should

apply the displayed value in your testbench parameters.

UG-01126

2015.05.04

Transceiver Reconfiguration Controller for Stratix V and Arria V GZ...

3-5

Getting Started

Altera Corporation