Source core link debugging, Source core link debugging -7 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 62

Source Core Link Debugging

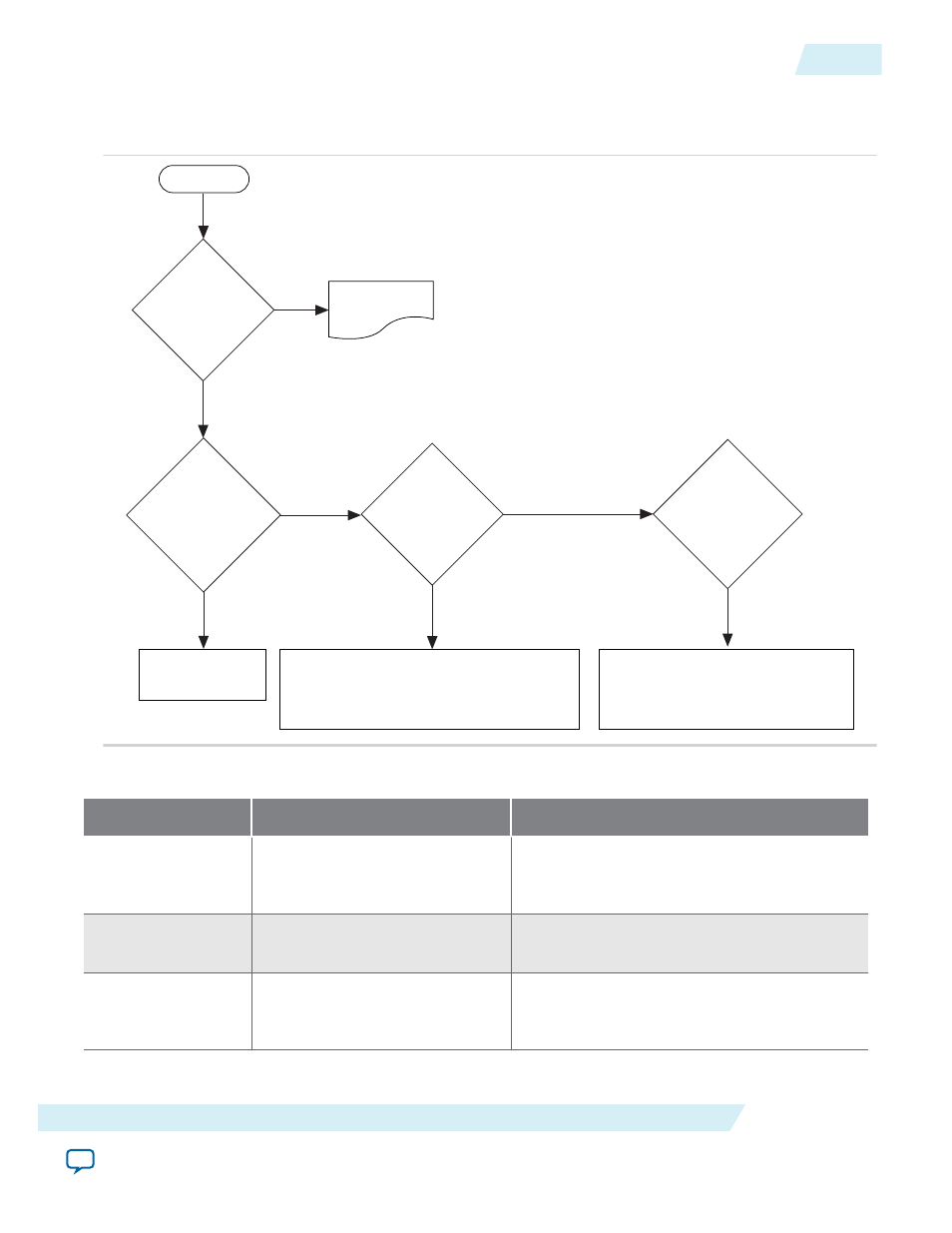

Figure 5-4: Source Core Link Debugging Flow Chart

Source Link

Iink_up asserted?

(Data pass through

to the transceivers?)

yes

no

tx_ready asserted?

(Are the transceivers

properly reset?)

yes

no

tx_sync_done

properly asserted?

(Are the channels

properly bonded?)

no

pll_lock asserted?

(Indicating that the

transceiver PLLs are

locked to input

frequency)

yes

no

Check Sink Link

Check the Transceiver

Reference Clock

-Make sure the Core clock is in between

lane-rate/40 and lane-rate/67

-Make sure that phy_mgmt_clk_reset remains

de-asserted

-Verify that the reconfiguration controller (RC)

is properly hooked up

-Make sure that the latencies of the reset going into the

RC and into the cores (phy_mgmt_clk_reset) are equal

Table 5-2: Source Link Debugging Signals

Signal Name

Location

Description

link_up

Top level source signal

The core asserts this signal to indicate that

initialization sequence is complete and the

core is ready to transmit the data.

xcvr_pll_locked

/source/xcvr_pll_locked

This active high signal indicates that the

transceivers are locked to the reference clock.

tx_ready

/source/tx_ready

This active high signal indicates that the reset

sequence for the source PCS is complete and is

ready to accept data.

UG-01126

2015.05.04

Source Core Link Debugging

5-7

SerialLite III Streaming IP Core Design Guidelines

Altera Corporation