Altera Cyclone III Development Board User Manual

Page 13

Chapter 2: Board Components

2–3

Board Overview

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

J5

Header

Speaker header.

D1, D3, D4

Ethernet PHY LEDs

Green Ethernet PHY LEDs. Illuminate when Ethernet PHY is using the

10/100/1000 Mbps (D1, D3, D4) connection speeds.

D6

Duplex Ethernet PHY

LED

Green Ethernet PHY LED. Illuminates when Ethernet PHY is both sending and

receiving data.

D5

Power LED

Blue LED indicates when power is applied to the board.

D7, D8

Ethernet PHY

transmit/receive activity

LEDs

Green LED. Illuminates when transmit/receive data is active from the Ethernet

PHY.

SW1

MAX II device control

DIP switch

Controls various features specific to the Cyclone III development board.

SW3

JTAG control switch

JTAG control DIP switch used to remove or include devices in the active JTAG

chain.

D17

SRAM active

SRAM active LED. Illuminates when the SRAM device is accessed.

D23

Flash active

Flash active LED. Illuminates when the flash device is accessed.

U28

Power display

Displays power measured by the MAX II CPLD.

D16

DDR2 LED

Indicates that the DDR2 top devices are active.

D11

DDR2 LED

Indicates that the DDR2 bottom devices are active.

Clock Circuitry

Y4

125 MHz

125-MHz clock oscillator used for the system clock.

Y5

50 MHz

50-MHz clock oscillator used for data processing.

Y1

24-MHz crystal

Cypress USB PHY.

Y2

6-MHz crystal

USB PHY FTDI reference clock.

Y3

24 MHz

MAX II device clock.

J10

SMA clock input

SMA connector that allows the provision of an external clock input.

J11

SMA clock output

SMA connector that allows the provision of an external clock output.

General User Input and Output

S1 through S4

User push buttons

Four 1.8-V push-button switches for user-defined, logic inputs.

S5

CPU reset push button

One 1.8-V push-button switch for FPGA logic and CPU reset.

S6 and S7

Reset and factory

configuration push

buttons

Two 1.8-V push-button switches that control FPGA configuration from flash

memory.

D26 through D33

User LEDs

Eight user-defined LEDs.

SW5

PGM CONFIG SELECT

Rotary switch to select which FPGA configuration file to use in flash memory.

SW4

Power select rotary

switch

Power rail select for on-board power monitor.

U30

User display

User-defined, green 7-segment display.

J4

Character LCD

14-pin LCD display.

J13

Graphics LCD

30-position dot matrix graphics LCD display.

Memory

U31

Flash

64 MB of flash memory with a 16-bit data bus.

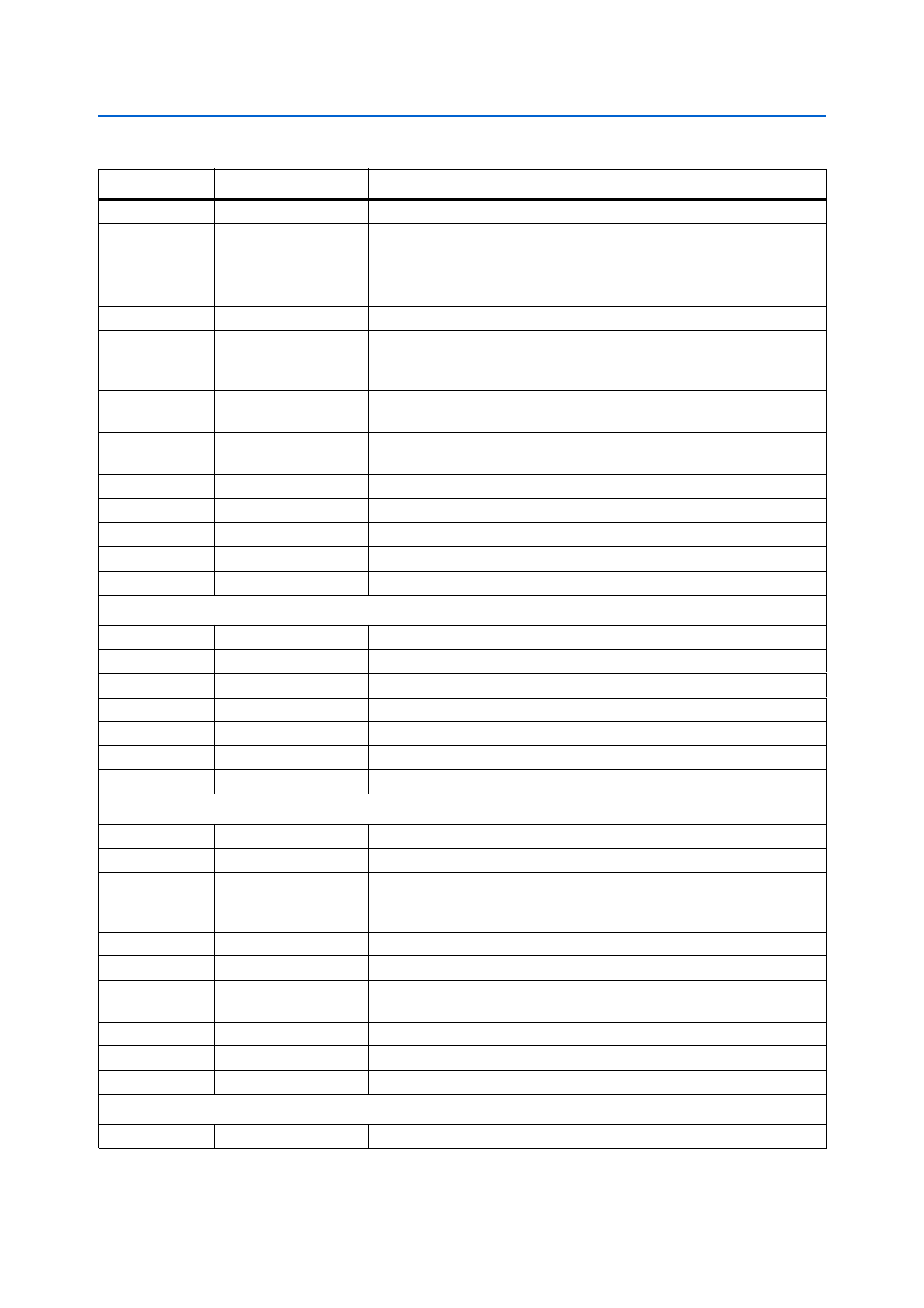

Table 2–1. Cyclone III Development Board (Part 2 of 3)

Board Reference

Type

Description