Max ii cpld, Max ii cpld –6, Figure 2–2 – Altera Cyclone III Development Board User Manual

Page 16

2–6

Chapter 2: Board Components

MAX II CPLD

Cyclone III 3C120 Development Board Reference Manual

© March 2009 Altera Corporation

MAX II CPLD

The board utilizes an Altera MAX II CPLD for the following purposes:

■

Power-up configuration of the FPGA from flash memory

■

Embedded USB-Blaster core for USB-based configuration of the FPGA

■

Power consumption monitoring and display

There are two USB MAC/PHY devices— FTDI and Cypress USB PHY devices— on

the board. They are muxed through the MAX II CPLD. Only one can operate at any

time. The FTDI device is the default device and it supports the embedded blaster

functionality. The Cypress USB PHY is held in reset and is reserved for future use.

Each device has a shared path between the USB device and the MAX II CPLD. The

individual paths then drive to the FPGA separately.

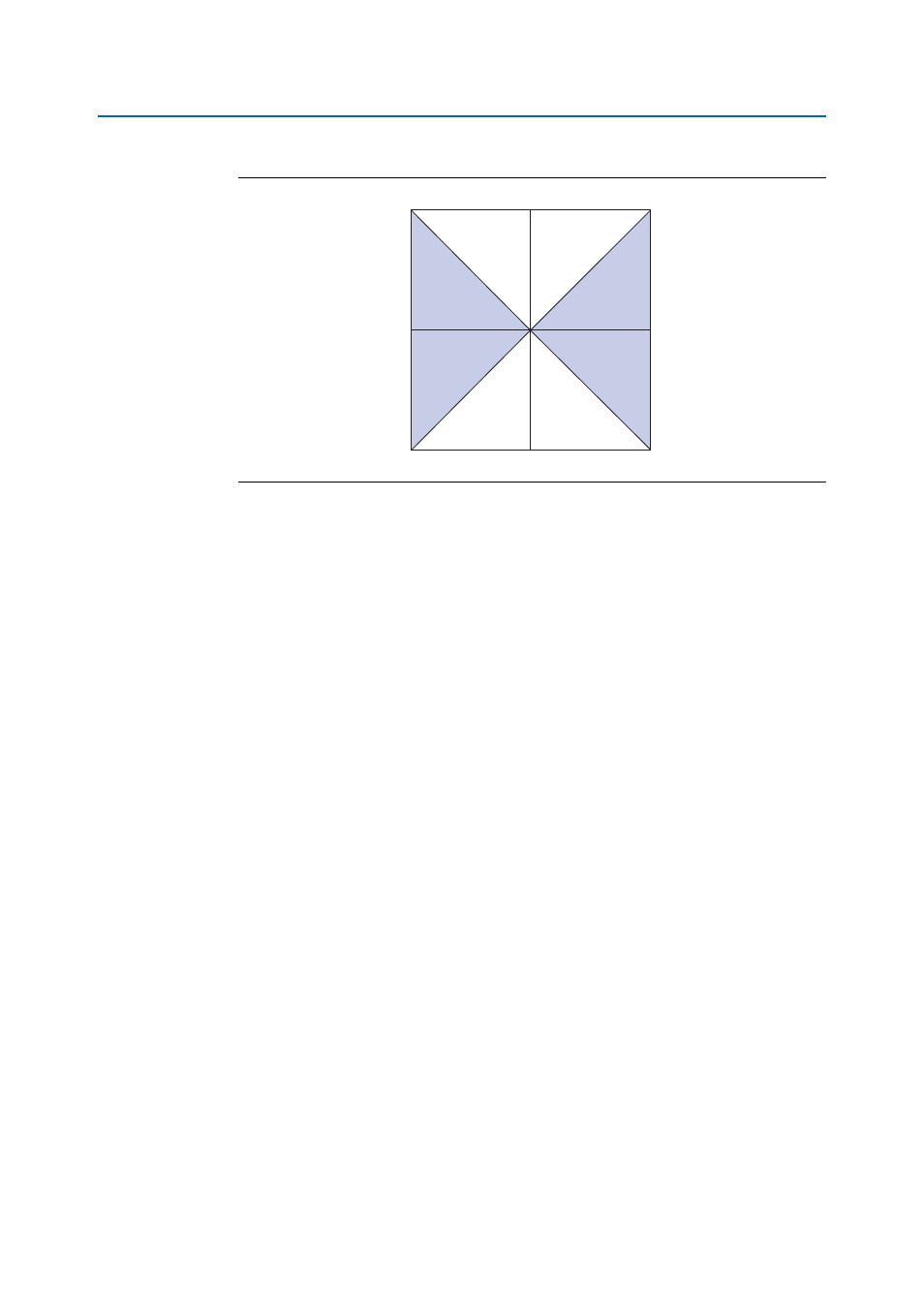

illustrates the MAX II

device’s block diagram.

Figure 2–2. Cyclone III Device I/O Bank Resources

B8

B7

72 I/O

72 I/O

73 I/O

71 I/O

B3

B4

58 I/O

B6

B5

B1

B2

63 I/O

58 I/O

65 I/O