Status elements, Flash programming over usb interface –17, Status elements –17 – Altera Cyclone III Development Board User Manual

Page 27: Board specific leds –17

Chapter 2: Board Components

2–17

Configuration, Status, and Setup Elements

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

Flash Programming over USB Interface

The flash memory can be programmed at any time the board is powered up by using

the USB 2.0 interface and the Quartus II Programmer ’s JTAG mode.

The development kit implements the Altera PFL megafunction for flash

programming. The PFL is a block of logic that is programmed into an Altera

programmable logic device (FPGA or CPLD). The PFL functions as a utility for

writing to a compatible flash device. The development kit ships with a pre-built PFL

design called cycloneIII_3c120_dev_pfl. The PFL design is programmed onto the

FPGA whenever the flash is to be written using the Quartus II software.

f

For more information about:

■

PFL megafunction, refer to

.

■

Basic flash programming instructions for the development board, refer to the

Programming the Flash Device section of the

Status Elements

The development board includes general user, board specific, and HSMC user LEDs.

This section discusses board-specific LEDs as well as the power display device.

f

For information about general and HSMC user-defined LEDS, refer to

Board Specific LEDs

There are 14 board-specific LEDs, which are factory designated.

lists the

LED board reference, name, and description.

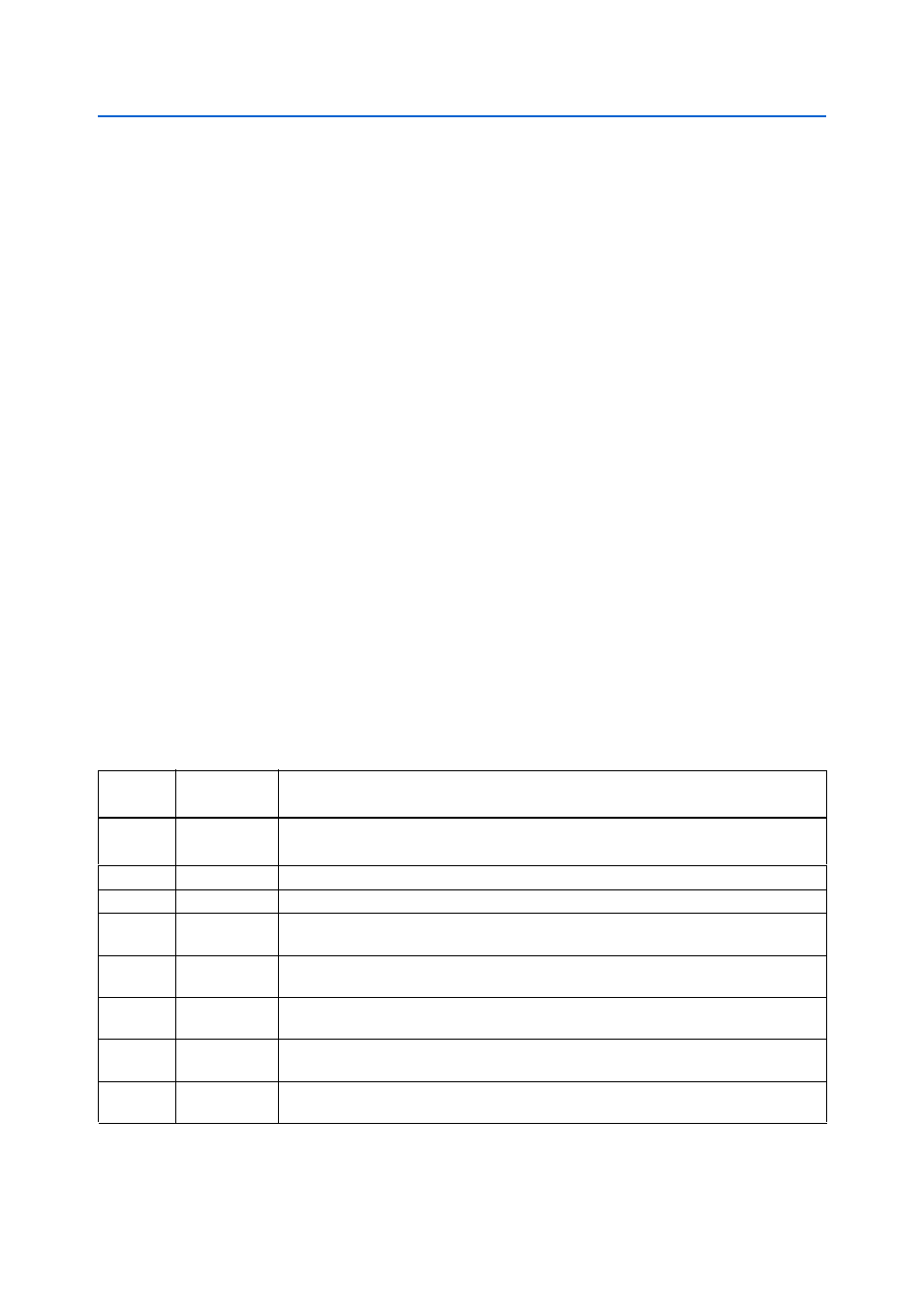

Table 2–8. Board-Specific LEDs (Part 1 of 2)

Board

Reference

LED Name

Description

D5

Power

Illuminates when board power switch SW2 is on.

(Requires 14 V to 20 V input to DC input jack J2)

D25

CONF DONE

Illuminates when FPGA is successfully configured. Driven by Cyclone III FPGA.

D20

Loading

Illuminates when MAX II CPLD is actively configuring the FPGA. Driven by the MAX II CPLD.

D21

Error

Illuminates when MAX II CPLD fails to successfully configure the FPGA. Driven by the

MAX II CPLD.

D24

Factory

Illuminates when FPGA is configured with the default factory FPGA design. Driven by the

MAX II CPLD.

D22

User

Illuminates when FPGA is configured with a design other than the default factory FPGA

design. Driven by the MAX II CPLD.

D7

ENET TX

Illuminates when transmit data is active from the Ethernet PHY. Driven by the

Marvell 88E1111 PHY.

D8

ENET RX

Illuminates when receive data is active from the Ethernet PHY. Driven by the

Marvell 88E1111 PHY.