Altera Cyclone III Development Board User Manual

Page 51

Chapter 2: Board Components

2–41

Communication Ports and Interfaces

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

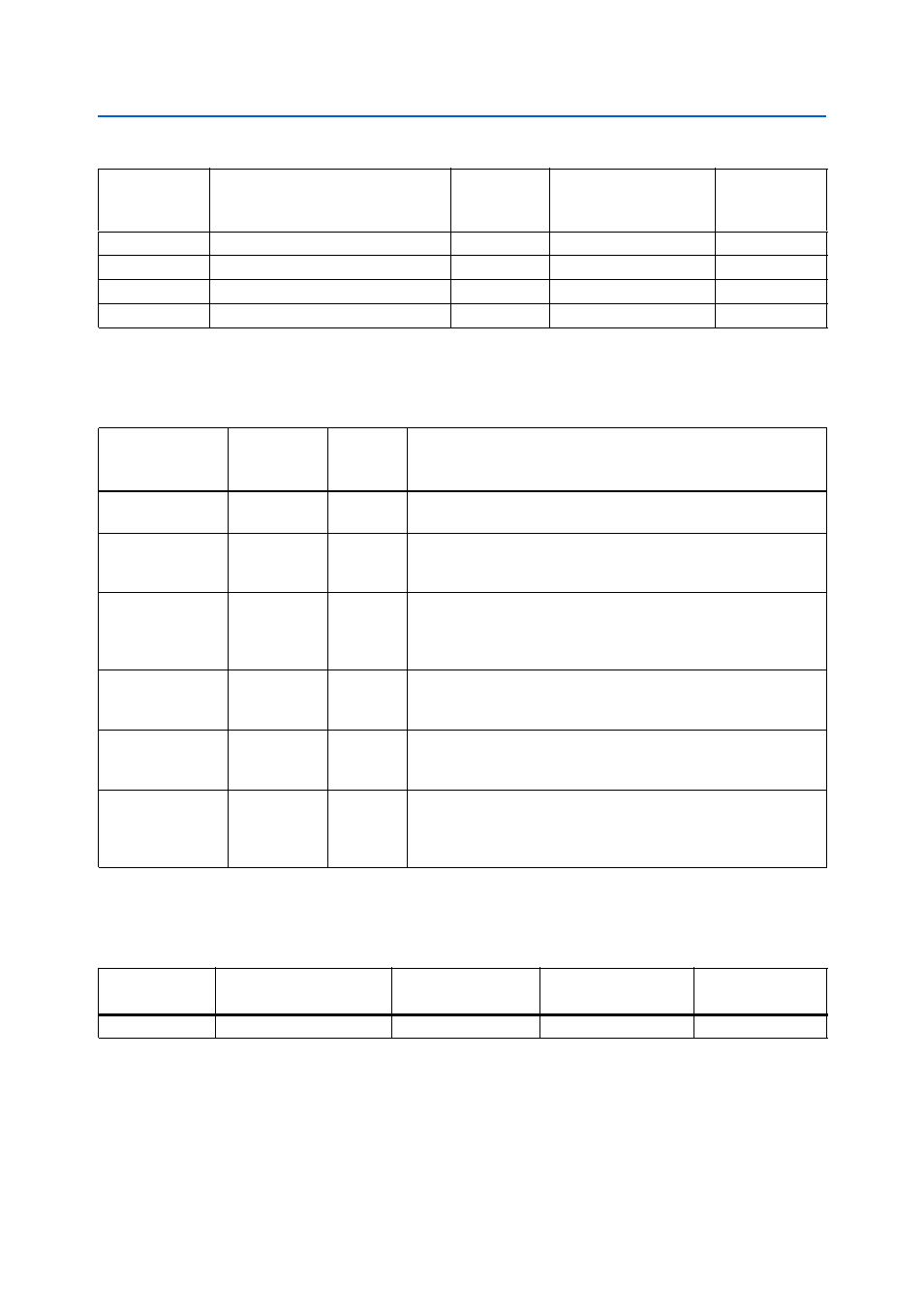

is an excerpt from the Marvell data sheet with a summary of RGMII

interface signals and their functions.

lists the 10/100/1000 Ethernet PHY component reference and

manufacturing information.

f

For more information about the data sheet and related documentation, contact

Marvell at

U5 pin 12

RGMII interface transmit data bus bit 1

2.5 V

ENET_TX_D1

AA5

U5 pin 14

RGMII interface transmit data bus bit 2

2.5 V

ENET_TX_D2

Y5

U5 pin 16

RGMII interface transmit data bus bit 3

2.5 V

ENET_TX_D3

W3

U5 pin 9

RGMII interface transmit control

2.5 V

ENET_TX_EN

AA7

Table 2–44. Ethernet PHY Interface I/O (Part 2 of 2)

Board

Reference

Description

I/O Standard

Schematic

Signal Name

Cyclone III

Device Pin

Number

Table 2–45. RGMII Signal Definitions

Schematic

Signal Name

Marvell

Device Pin

Name

RGMII

Spec Pin

Name

Description

ENET_GTX_CLK

GTX_CLK

TXC

125-MHz, 25-MHz, or 2.5-MHz transmit clock with ±50 ppm tolerance

based on the selected speed.

ENET_TX_EN

TX_EN

TX_CTL

Transmit control signals. TX_EN is encoded on the rising edge of

GTX_CLK

, TX_ER, XORed with TX_EN is encoded on this falling

edge of GTX_CLK.

ENET_TXD[3:0]

TXD[3:0]

TD[3:0]

Transmit data. In 1000 base-T and 1000 base-X modes, TXD[3:0]

are presented on both edges of GTX_CLK. In 100 base-T and 10

base-T modes, TXD[3:0] are presented on the rising edge of

GTX_CLK

.

ENET_RX_CLK

RX_CLK

RXC

125-MHz, 25-MHz, or 2.5-MHz receive clock ±50 ppm tolerance

derived from the received data stream and based on the selected

speed.

ENET_RX_DV

RX_DV

RX_CTL

Receive control signals. RX_DV is encoded on the rising edge of

RX_CLK

, RX_ER XORed with RX_DV is encoded on the falling

edge of RX_CLK.

ENET_RXD[3:0]

RXD[3:0]

RD[3:0]

Receive data. In 1000 base-T and 1000 base-X modes, RXD[3:0]

are presented on both edges of RX_CLK. In 100 base-TX and 10

base-T modes, RXD[3:0] are presented on the rising edge of

RX_CLK

.

Table 2–46. Ethernet PHY Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U5

Ethernet PHY Base-T device

Marvell Semiconductor 88E1111-B2-CAA1C000