Cyclone iii fpga clock outputs, Cyclone iii fpga clock outputs –24 – Altera Cyclone III Development Board User Manual

Page 34

2–24

Chapter 2: Board Components

Clocking Circuitry

Cyclone III 3C120 Development Board Reference Manual

© March 2009 Altera Corporation

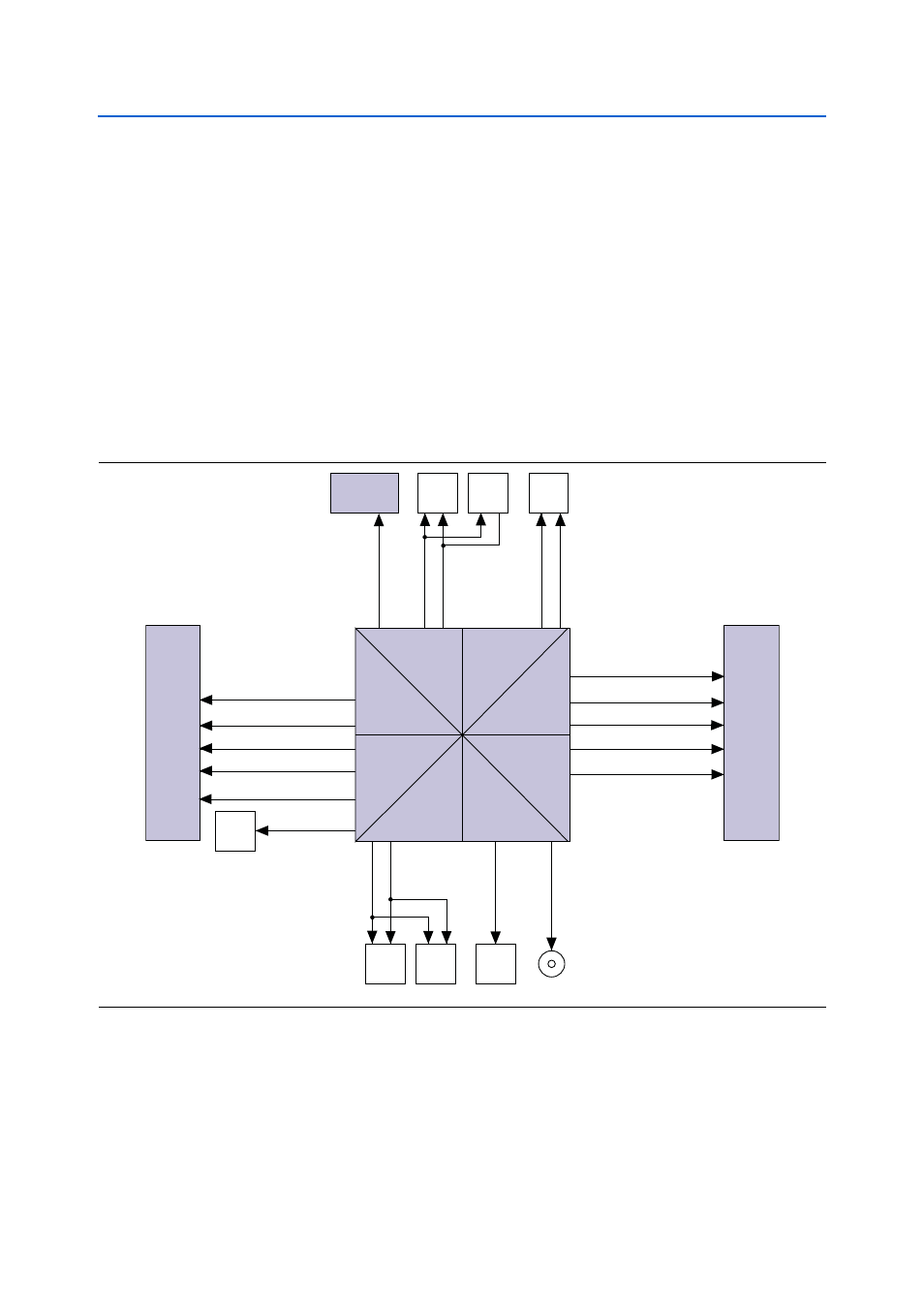

Cyclone III FPGA Clock Outputs

outlines the clocking outputs from the Cyclone III FPGA.

1

Some signals are connected to 1.8-V banks and some are connected to 2.5-V banks.

Refer to the

for information about voltage output levels.

The clock 1 and clock 2 signals from the HSMC interface can be used as LVDS pairs or

as eight separate clock signals. These signals include HSMA_CLK_IN_P2/N2,

HSMA_CLK_IN_P1/N1

, HSMB_CLK_IN_P2/N2, and HSMB_CLK_IN_P1/N1. These

signals may also be used for bidirectional data.

The CLKOUT_SMA signal connects to the Cyclone III FPGA using a dedicated PLL

output pin, PLL4_CLKOUTp. This pin does not have to be used with the PLL as it can

also drive data or other trigger signals.

shows the clocking parts list.

Figure 2–6. Cyclone III FPGA Clock Outputs

Bank 8

1.8 V

Bank 7

1.8 V

Bank 3

1.8 V

Bank 4

1.8 V

Bank 6

2.5 V

Bank 5

2.5 V

Bank 1

2.5 V

Bank 2

2.5 V

HSMC

Port A

ENET

PHY

DDR2

DDR2

SRAM

HSMA_CLK_OUT_P2

HSMA_CLK_OUT_N2

HSMA_CLK_OUT_P1

HSMA_CLK_OUT_N1

DDR2_CK_P0

HSMA_CLK_OUT0

HSMC

Port B

HSMB_CLK_OUT_IN0

HSMB_CLK_IN_P1

HSMB_CLK_IN_N1

HSMA_CLK_IN_P2

HSMA_CLK_IN_N2

ENET_GTX_CLK

SRAM_CLK

CLK

OUT_SMA

DDR2_CK_N0

DDR2

DDR2

DDR2

PLL4

DDR2_CK_P2

DDR2_CK_P2

DDR2_CK_N2

MAX II CPLD

MAX2_CLK

DDR2_CK_N1

SMA Output