Fpga programming from flash memory –16, Table 2–7 – Altera Cyclone III Development Board User Manual

Page 26

2–16

Chapter 2: Board Components

Configuration, Status, and Setup Elements

Cyclone III 3C120 Development Board Reference Manual

© March 2009 Altera Corporation

FPGA Programming from Flash Memory

On either power-up or by pressing the RESET_CONFIG or FACTORY_CONFIG push

button, the MAX II CPLD device’s PFL megafunction configures the Cyclone III

FPGA from flash memory.

The PFL megafunction reads 16-bit data from the flash memory and converts it to

passive serial format. The data is written to the Cyclone III device’s dedicated DCLK

and D0 configuration pins at 12 MHz.

FPGA configuration from flash memory can be sourced from one of eight images. The

image is selected by the PGM_CONFIG_SELECT rotary switch, board reference SW5.

The rotary switch has 16 positions, but only the first eight are used. The positions

correspond to an offset in flash memory that the PFL is directed to for FPGA

configuration data.

1

Board reference SW1 position 5 (SW1.5), labeled MAX0, must be in the

open position (1) for this feature to be enabled. If the SW1 switch is in the closed (0)

position, the PFL megafunction in the MAX II CPLD is disabled.

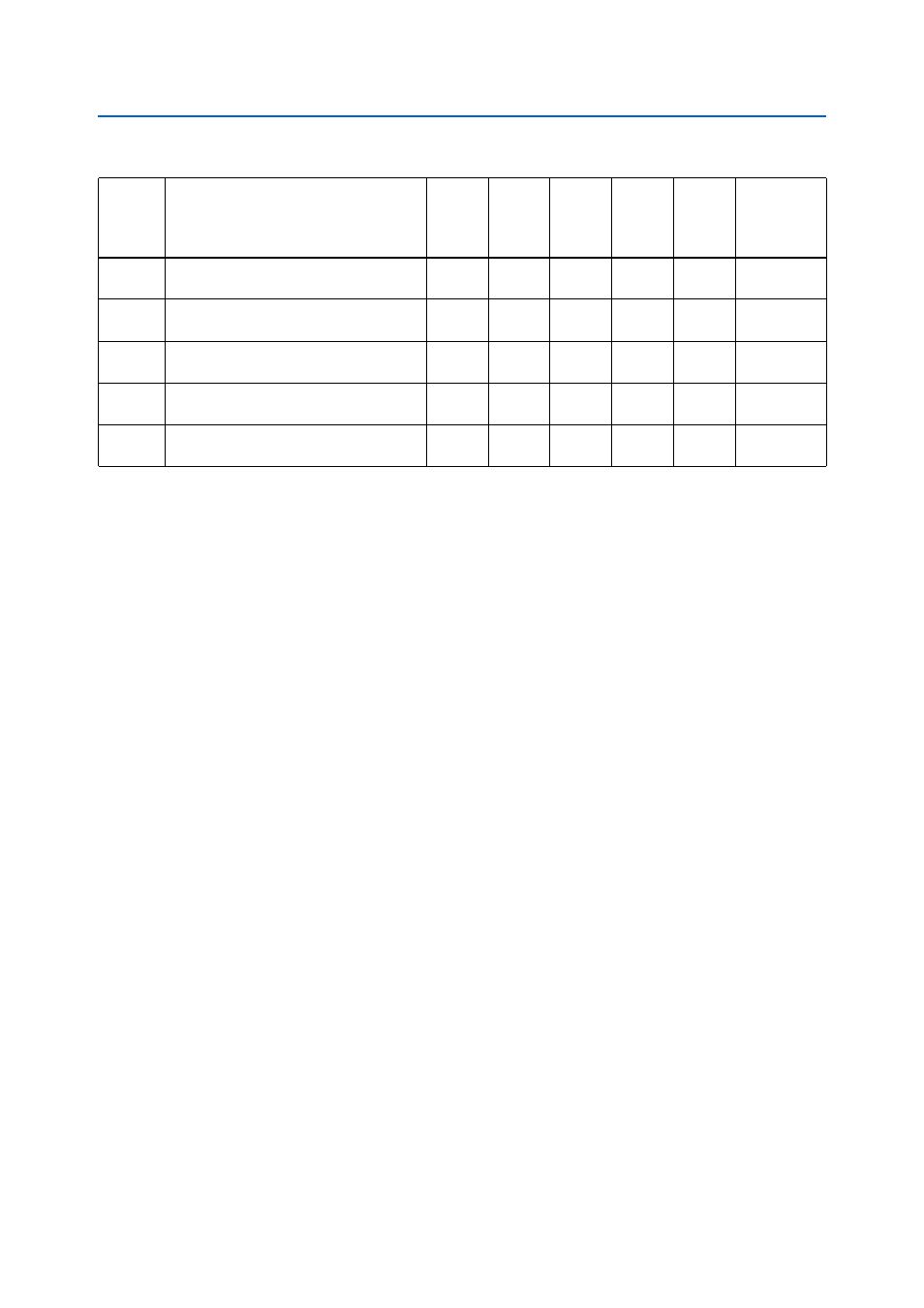

Number

Description

FPGA

Bypass

(SW3.1)

HSMA

Bypass

(SW3.2)

HSMB

Bypass

(SW3.3)

MAX

Enable

(SW3.4)

PFL

Enable

(SW1.5

MAX0)

Device

Select

(DEV_SEL)

Jumper, J6

1

Cyclone III target device only

1

0

0

0

1

X

2

Cyclone III device + HSMC Port A

1

1

0

0

1

X

3

Cyclone III device + HSMC Port B

1

0

1

0

1

X

4

,

Cyclone III target device only

X

X

X

1

1

Off

5

,

MAX II target device only

X

X

X

X

X

On

(1) The nomenclature SW3.1 is used to indicate board reference SW3, position 1; similarly SW1.5 is used to indicate board reference SW1,

position 5.

(2) Requires USB cable plugged into board reference J3.

(3) Requires external USB-Blaster or equivalent plugged into board reference J14 (PCB bottom).

(4) The JTAG chains for both HSMC ports A and B can only be accessed from the embedded USB-Blaster. They cannot be accessed from the

external USB-Blaster header.