Altera Cyclone III Development Board User Manual

Page 63

Chapter 2: Board Components

2–53

On-Board Memory

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

lists the DDR2 interface component reference and manuf

acturing

information.

U11, U12 pin P7, U13 pin K7

Top address 11

SSTL18 Class 1

DDR2TOP_A11

D8

U11, U12 pin R2, U13 pin L2

Top address 12

SSTL18 Class 1

DDR2TOP_A12

D25

U11, U12 pin R8, U13 pin L8

Top address 13

SSTL18 Class 1

DDR2TOP_A13

F15

U11, U12 pin R3, U13 pin L3

Top address 14

SSTL18 Class 1

DDR2TOP_A14

B12

U11, U12 pin R7

Top address 15

SSTL18 Class 1

DDR2TOP_A15

H16

U11, U12 pin M7, U13 pin H7

Top address 2

SSTL18 Class 1

DDR2TOP_A2

E8

U11, U12 pin N2, U13 pin J2

Top address 3

SSTL18 Class 1

DDR2TOP_A3

D24

U11, U12 pin N8, U13 pin J8

Top address 4

SSTL18 Class 1

DDR2TOP_A4

D7

U11, U12 pin N3, U13 pin J3

Top address 5

SSTL18 Class 1

DDR2TOP_A5

J15

U11, U12 pin N7, U13 pin J7

Top address 6

SSTL18 Class 1

DDR2TOP_A6

H15

U11, U12 pin P2, U13 pin K2

Top address 7

SSTL18 Class 1

DDR2TOP_A7

J16

U11, U12 pin P8, U13 pin K8

Top address 8

SSTL18 Class 1

DDR2TOP_A8

H8

U11, U12 pin P3, U13 pin K3

Top address 9

SSTL18 Class 1

DDR2TOP_A9

D16

LED D11 pin 2

Top bus activity LED

1.8 V

DDR2TOP_ACTIVE

E10

U11, U12 pin L2, U13 pin G2

Top bank address 0

SSTL18 Class 1

DDR2TOP_BA0

C23

U11, U12 pin L3, U13 pin G3

Top bank address 1

SSTL18 Class 1

DDR2TOP_BA1

D19

U11, U12 pin L1, U13 pin G1

Top bank address 2

SSTL18 Class 1

DDR2TOP_BA2

C26

U11, U12 pin L7, U13 pin G7

Top column address

strobe

SSTL-18 Class I

DDR2TOP_CASn

F14

U11, U12 pin K2, U13 pin F2

Top clock enable

SSTL-18 Class I

DDR2TOP_CKE

E21

U11, U12 pin L8, U13 pin G8

Top chip select

SSTL-18 Class I

DDR2TOP_CSn

C7

U11, U12 pin K9, U13 pin F9

Top on-die termination

enable

SSTL-18 Class I

DDR2TOP_ODT

A6

U11, U12 pin K7, U13 pin F7

Top row address strobe

SSTL-18 Class I

DDR2TOP_RASn

F8

U11, U12 pin K3, U13 pin F3

Top write enable

SSTL-18 Class I

DDR2TOP_WEn

A10

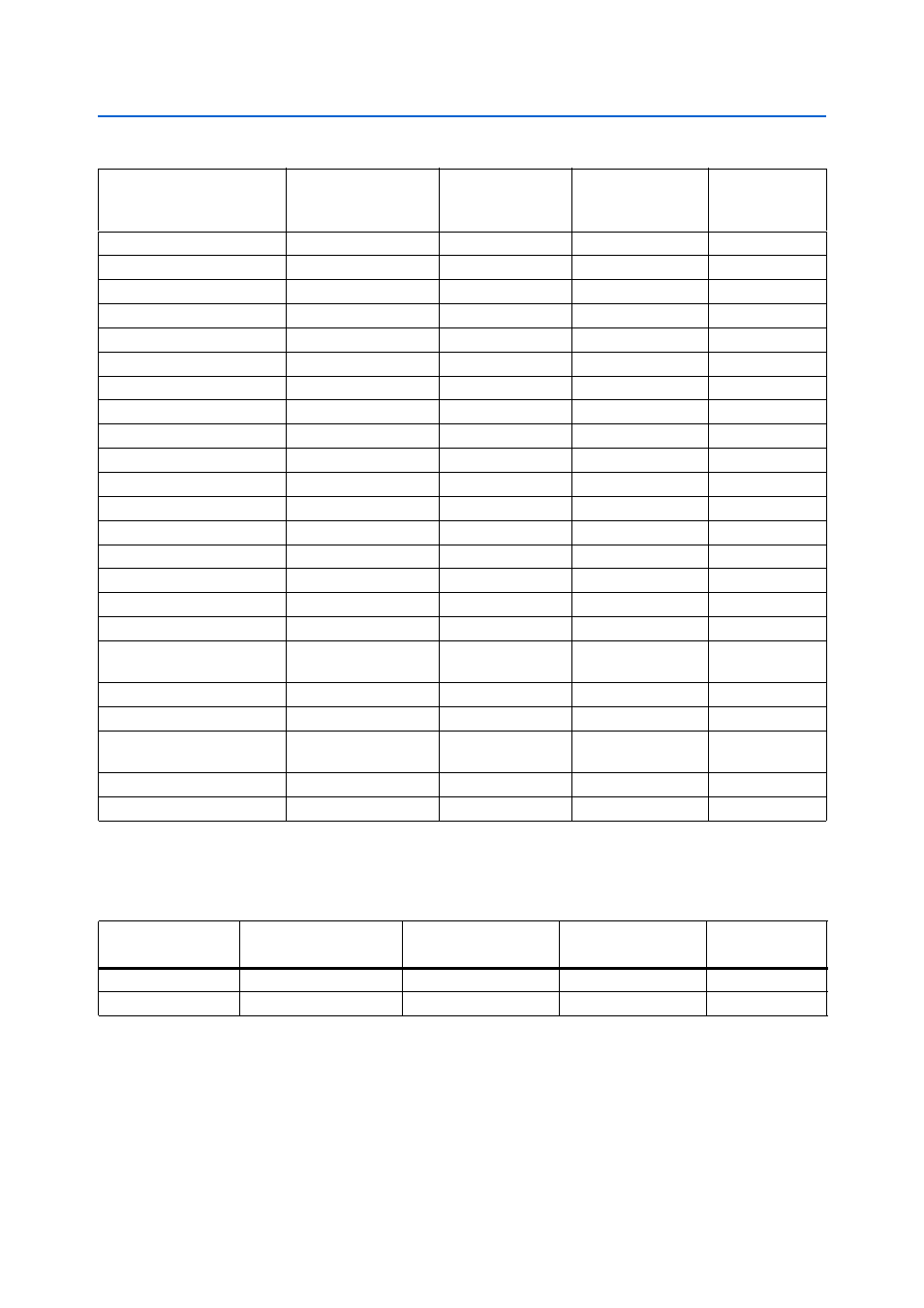

Table 2–51. DDR2 Interface I/O (Part 5 of 5)

Board

Reference

Description

I/O Standard

Schematic

Signal Name

Cyclone III

Device Pin

Number

Table 2–52. DDR2 Interface Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U11, U12, U25, U26

DDR2 SDRAM 34 M × 16

Micron Technology, Inc.

MT47H32M16CC-3:B

U13

DDR2 SDRAM 32 M × 8

Micron Technology, Inc.

MT47H32M8BP-3:B