Altera Cyclone III Development Board User Manual

Page 49

Chapter 2: Board Components

2–39

Communication Ports and Interfaces

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

lists the FTDI USB interface pins. Signal name and direction are relative to

the MAX II CPLD.

lists the FTDI USB interface component reference and manufacturing

information.

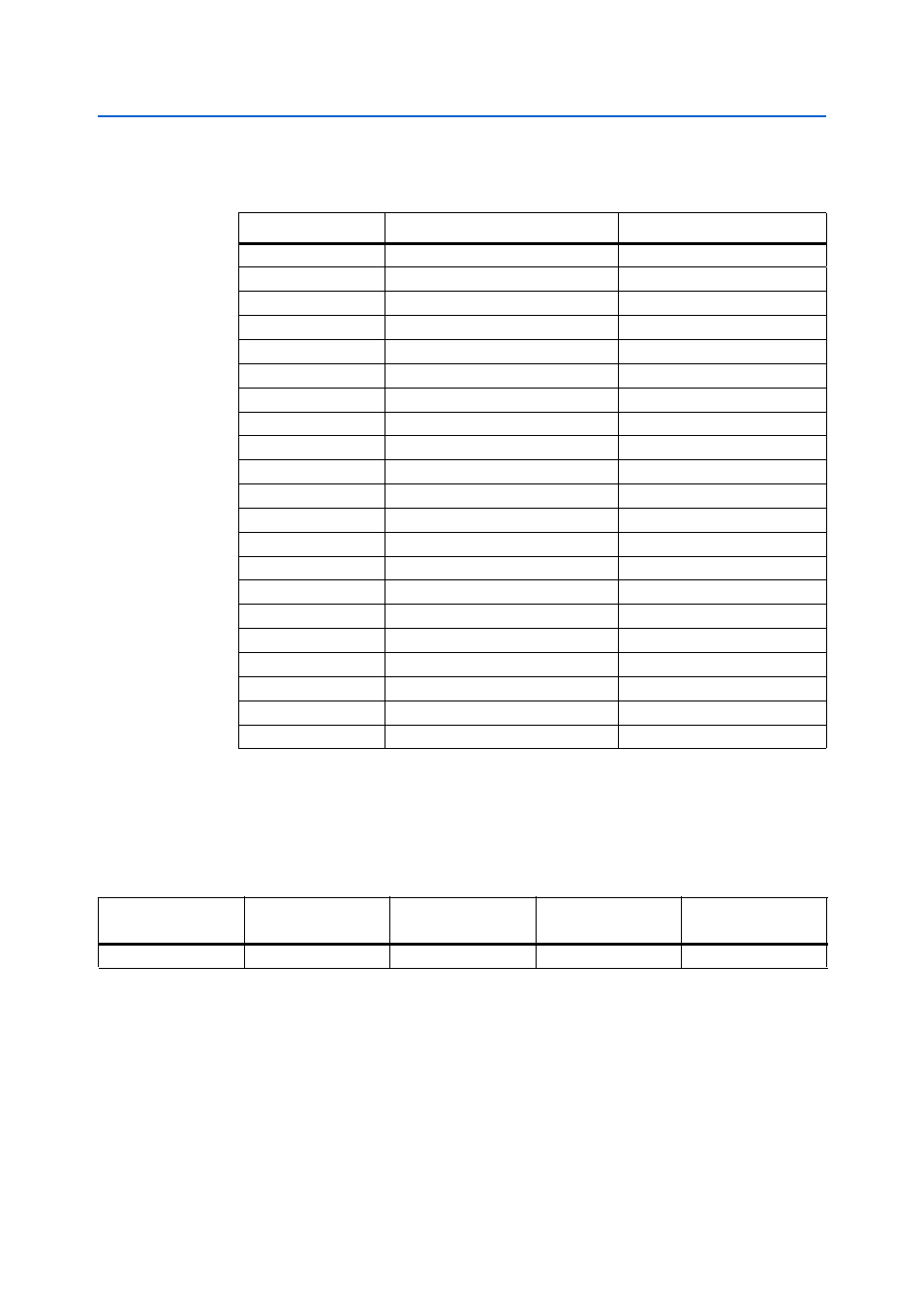

Table 2–42. FTDI USB PHY Interface I/O

Signal Names

Description

Type

USB_FD(7:0)

FIFO data bus

2.5-V CMOS in/out (8 bit)

USB_RDn

FIFO data bus read enable

2.5-V CMOS in

USB_WR

FIFO data bus write enable

2.5-V CMOS in

USB_RXFn

FIFO data bus RX enable

2.5-V CMOS out

USB_TXEn

FIFO data bus TX enable

2.5-V CMOS out

USB_EECS

EEPROM select

N/A

USB_EESK

EEPROM clock

N/A

USB_EEDATA

EEPROM dData

N/A

USB_DP

USB PHY +

N/A

USB_DM

USB PHY –

N/A

USB_RSTn

Reset in

2.5-V CMOS output

USB_RSTOUTn

Reset out

2.5-V CMOS input

USB_XTIN

6-MHz crystal input

N/A

USB_XTOUT

6-MHz crystal output

N/A

USB_PWRENn

Power enable

2.5-V CMOS input

USB_SI_WU

Send immediate / wake up

VCC

5-V core power

5.0 V (powered by USB host)

VCCIO

I/O power

3.3 V

AVCC

Analog power

1.2 V

AGND

Analog ground

1.2 V

GND

Ground

Ground

Note to

(1) The FTDI USB 2.0 device uses 3.3-V LVTTL levels driving into 2.5-V I/O banks on the MAX II CPLD.

Table 2–43. FTDI Interface Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Web Site

U8

FTDI USB device

FTDI Ltd

FT245BL