Altera Stratix II GX PCI Express Development Board User Manual

Page 39

Altera Corporation

Reference Manual

2–29

August 2006

Stratix II GX PCI Express Development Board

Board Components & Interfaces

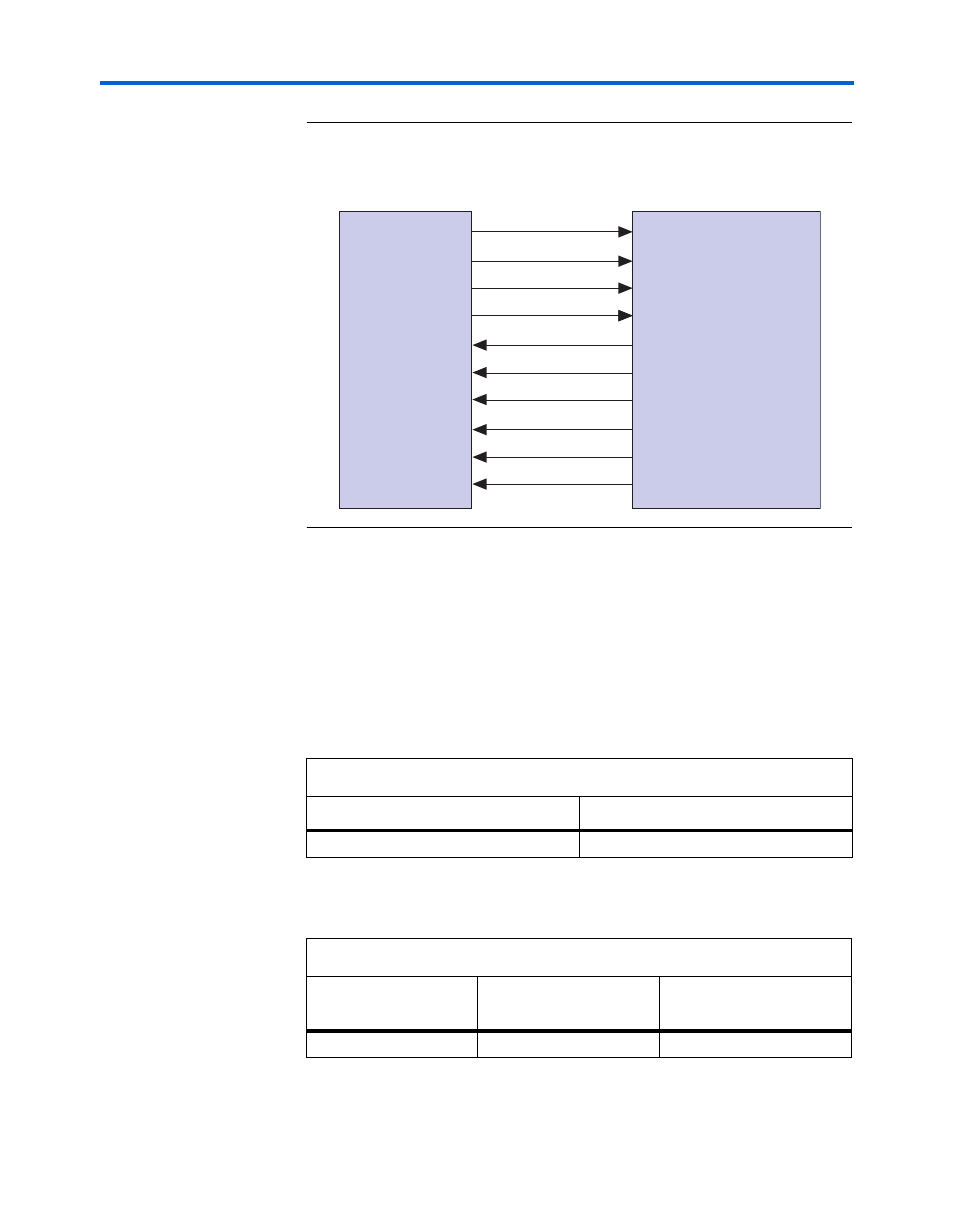

Figure 2–11. Marvell 88E1111 GigE PHY Layer & GMII Interface to the FPGA

f

For more information about the Stratix II GX Gigabit Ethernet MAC

megafunction, please refer to the following:

■

Stratix II GX Embedded Ethernet MAC/PHY Users Guide (Verilog HDL)

■

Stratix II GX Embedded Ethernet MAC/PHY Users Guide (VHDL)

■

Stratix II GX Handbook

lists the RJ-45 jack board reference and description.

Table 2–21

lists manufacturing information.

GTX_CLK

TX_ER

TX_EN

TXD[7:0]

GTX_CLK

Stratix II GX

MAC Block

Marvell 88E1111

GigE PHY Layer

TX_ER

TX_EN

TXD[7:0]

RX_CLK

RX_ER

RX_DV

RX_CLK

RX_ER

RX_DV

RXD[7:0]

CRS

COL

RXD[7:0]

CRS

COL

GMII Interface

Table 2–20. Component Reference RJ-45 Jack

Board Reference

Device Description

RJ1

RJ-45 single-port jack

Table 2–21. Manufacturing Information

Manufacturer

Manufacturer Part

Number

Manufacturer Website

HALO Electronics

HFJ11-1G02E

www.haloelectronics.com