Off-chip memory, Ddr2 sdram, Off-chip memory -44 – Altera Stratix II GX PCI Express Development Board User Manual

Page 54: Ddr2 sdram -44

2–44

Reference Manual

Altera Corporation

Stratix II GX PCI Express Development Board

August 2006

Off-Chip Memory

Off-Chip

Memory

This section describes the board’s off-chip memory interface support,

providing signal type and signal connectivity relative to the Stratix II GX

device.

The board supports the following off-chip memory interfaces:

■

DDR2 SDRAM

■

QDRII SRAM

DDR2 SDRAM

The board features a 72-bit double-data-rate (DDR2) synchronous

dynamic random access memory (SDRAM) interface. The 72-bit interface

is made up of four x16 devices for the 64-bit datapath and a single x8

device for the ECC bits. The maximum speed is 333-MHz DDR for a total

theoretical bandwidth of nearly 48 Gb/s. The DDR interface signals have

a single 56

Ω termination. Resistors tied to a termination voltage of 0.9 V

are called VTT. This termination scheme is referred to as Class I

termination. The DDR2 components also provide an optional on-chip

termination of 50, 75, or 150

Ω.

lists DDR2 SRAM component reference and manufacturing

information.

lists DDR2 SRAM pin-out as well as corresponding

Stratix II GX pin numbers.

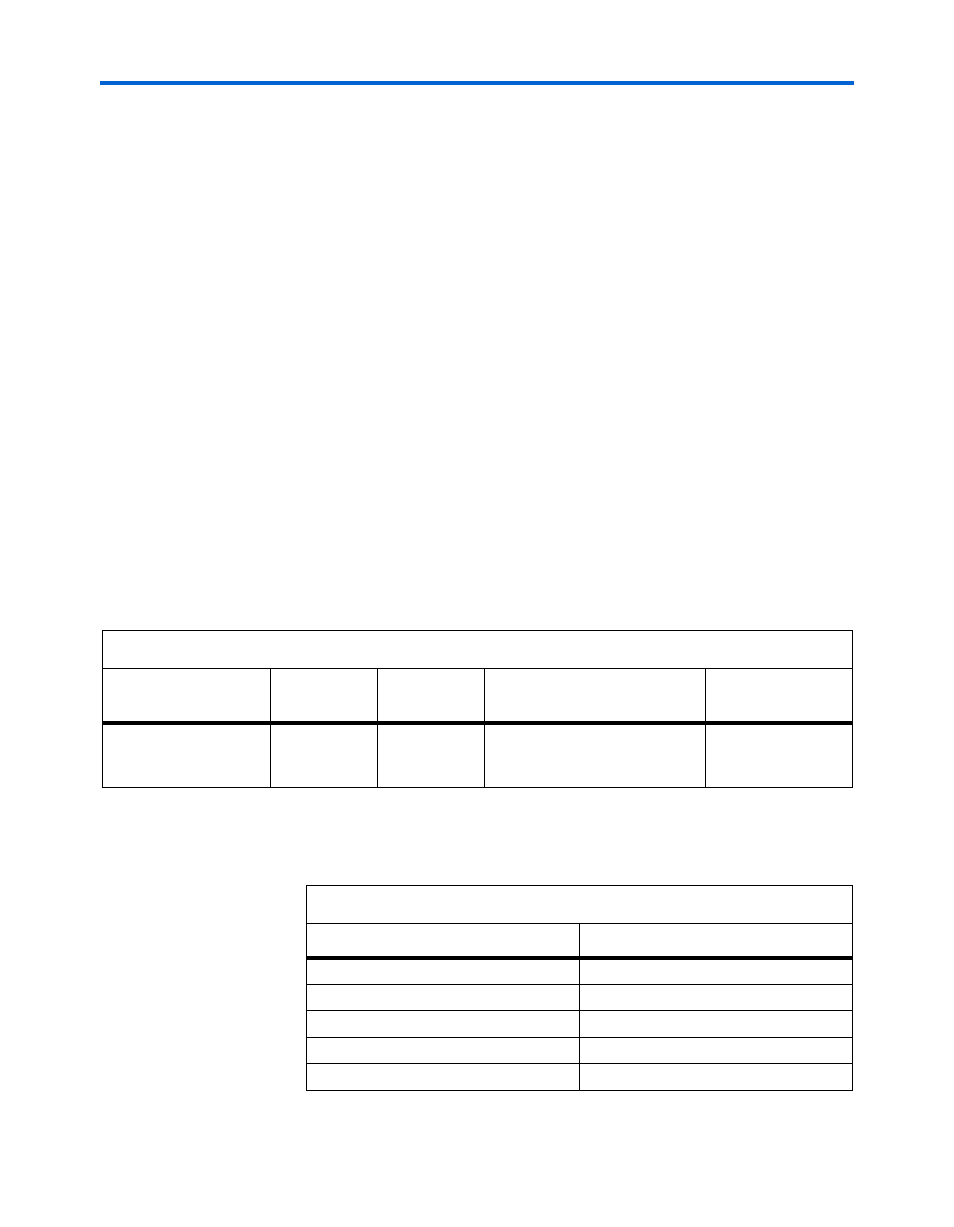

Table 2–29. DDR2 Component Reference and Manufacturing Information

Board Reference

Device

Description

Manufacturer

Manufacturer

Part Number

Manufacturer

Website

U2, U5, U8, U11, U13

333 MHz

DDR2

SDRAM

Micron MT47H32M16CC-3

32Mx16

(U5, U8, U11, U13);

MT47H64M8CB-3 32Mx8 (U2)

www.micron.com

Table 2–30. DDR2 SRAM Pin-Out (Part 1 of 5)

Schematic Signal Name

Stratix II GX Device Pin Number

ddr2_a[0]

AP16

ddr2_a[1]

AH28

ddr2_a[10]

AT30

ddr2_a[11]

AN21

ddr2_a[12]

AP28