Qdrii sram, Qdrii sram -49 – Altera Stratix II GX PCI Express Development Board User Manual

Page 58

2–48

Reference Manual

Altera Corporation

Stratix II GX PCI Express Development Board

August 2006

Off-Chip Memory

QDRII SRAM

The board uses a burst-of-four QDRII SRAM memory device for

high-speed, low-latency memory access, with addressing for up to a

72-MB device.

The QDRII device has separate read and write data ports with DDR

interfaces at up to 300 MHz. Burst-of-4 devices have higher data rates due

to the longer sequential addressing. The QDRII interface supports over

21 Gb/s of throughput at 300 MHz (600 MB/s x 36 pins). The bandwidth

doubles to over 42 Gb/s when combined read and write bandwidths are

considered.

The QDRII interface signals do not have board-level termination

resistors. Instead, the QDRII interface is terminated using the 50

Ω output

impedance settings available on both the Stratix II GX device and the

QDRII SRAM device. This approach simplifies board routing and lowers

power consumption.

ddr2_dqs[1]

AU12

ddr2_dqs[2]

AT14

ddr2_dqs[3]

AP15

ddr2_dqs[4]

AV18

ddr2_dqs[5]

AU23

ddr2_dqs[6]

AT25

ddr2_dqs[7]

AU28

ddr2_dqs[8]

AW33

ddr2_odt

AN25

ddr2_rasn

AJ27

ddr2_sync_clk_in

AW20

ddr2_sync_clk_out

AV36

ddr2_wen

AL13

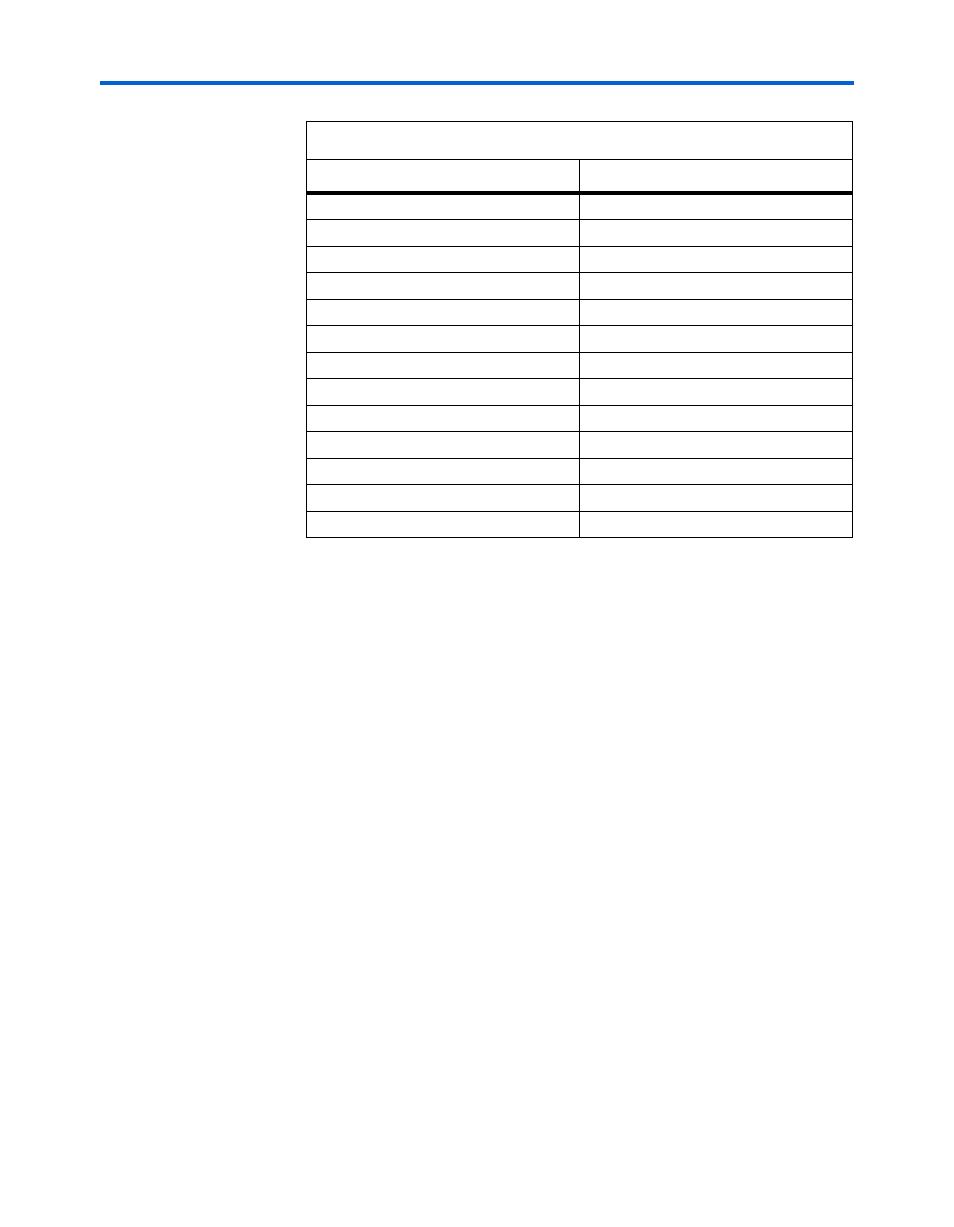

Table 2–30. DDR2 SRAM Pin-Out (Part 5 of 5)

Schematic Signal Name

Stratix II GX Device Pin Number