Altera PCI Compiler User Manual

Page 139

Altera Corporation

User Guide Version 11.1

3–65

October 2011

Functional Description

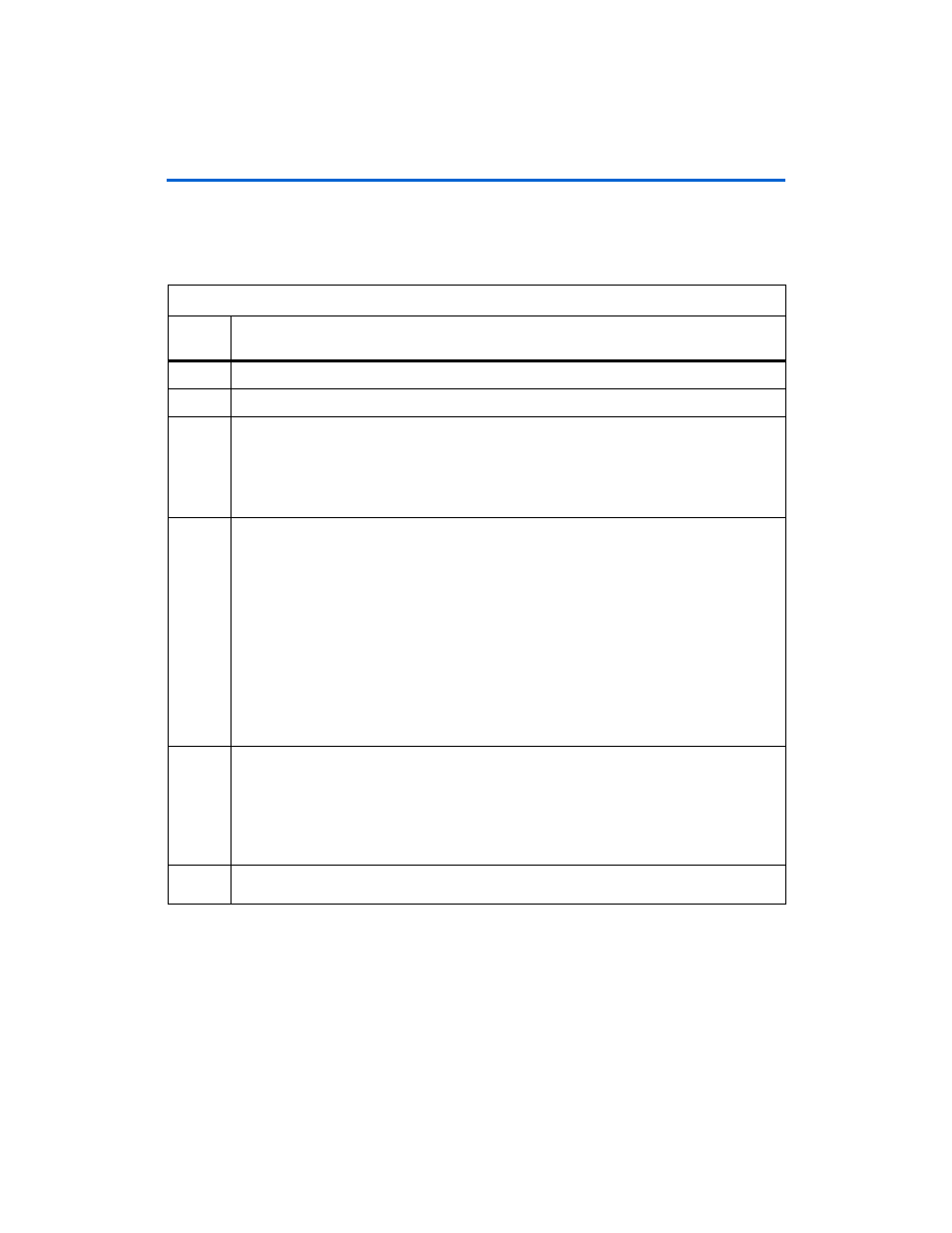

shows the sequence of events for a 64-bit single-cycle memory

write target transaction. The 64-bit extension signals are not applicable to

the pci_mt32 and pci_t32 MegaCore functions.

Table 3–36. Single-Cycle Memory Write Target Transactions (Part 1 of 2)

Clock

Cycle

Event

1

The PCI bus is idle.

2

The address phase occurs.

3

The PCI MegaCore function latches the address and command, and decodes the address to check

if it falls within the range of one of its BARs. During clock cycle 3, the master deasserts the

framen

and

req64n

signals and asserts

irdyn

to indicate that only one data phase remains in the

transaction. For a single-cycle memory write target transaction, this phase is the only data phase in

the transaction. The MegaCore function uses clock cycle 3 to decode the address, and if the address

falls in the range of one of its BARs, the transaction is claimed.

4

If the PCI MegaCore function detects an address hit in clock cycle 3, several events occur during

clock cycle 4:

●

The PCI MegaCore function informs the local-side device that it is going to claim the write

transaction by asserting

lt_framen

and the bit on

lt_tsr[5..0]

that corresponds to the

BAR range hit. In

,

lt_tsr[0]

is asserted indicating that a base address register

zero hit.

●

The PCI MegaCore function drives the transaction command on

l_cmdo[3..0]

and address

on

l_adro[31..0]

.

●

The PCI MegaCore function turns on the drivers of

devseln

,

ack64n

,

trdyn

, and

stopn

getting ready to assert

devseln

and

ack64n

in clock cycle 5.

●

lt_tsr[7]

is asserted to indicate that the pending transaction is 64 bits.

●

lt_tsr[8]

is asserted to indicate that the PCI side of the PCI MegaCore function is busy.

5

The PCI MegaCore function asserts

devseln

to claim the transaction.

also shows the

local side asserting

lt_rdyn

, indicating that it is ready to receive data from the PCI MegaCore

function in clock cycle 6.

To allow the local side ample time to issue a retry for the write cycle, the PCI MegaCore function does

not assert

trdyn

in the first data phase unless the local side asserts

lt_rdyn

. If

lt_rdyn

is not

asserted in clock cycle 5 (

), the PCI MegaCore function delays the assertion of

trdyn

.

6

The PCI MegaCore function asserts

trdyn

to inform the PCI master that it is ready to accept data.

Because

irdyn

is already asserted, this clock cycle is the first and last data phase in this cycle.