Altera PCI Compiler User Manual

Page 71

Altera Corporation

User Guide Version 11.1

2–13

October 2011

Parameter Settings

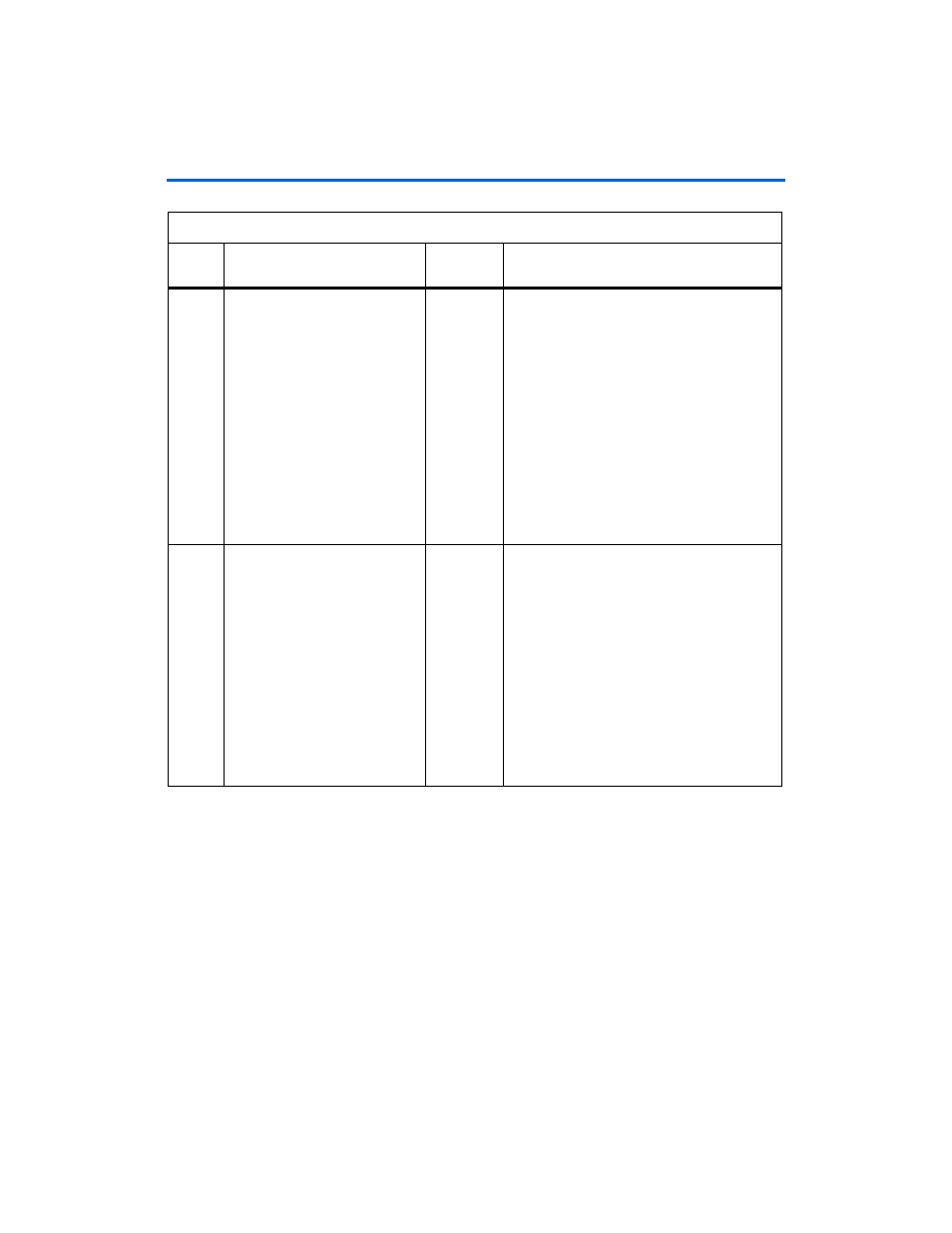

13

SELF_CFG_HB_ENA (1)

0

Host bridge enable. This bit controls the self-

configuration host bridge functionality. Setting this

bit to 1 causes the

pci_mt64

and

pci_mt32

MegaCore functions to power up with the master

enable bit in the command register hardwired to 1

and allows the master interface to initiate

configuration read and write transactions to the

internal configuration space. This feature does

not need to be enabled for the

pci_mt64

or

pci_mt32

master to initiate configuration read

and write transactions to other agents on the PCI

bus. Finally, you will still need to connect IDSEL

to one of the high order bits of the AD bus as

indicated in the PCI Local Bus Specification,

version 3.0 to complete configuration

transactions.

14

LOC_HDAT_MUX_ENA

0

Add internal data steering logic for 32- and 64-bit

systems. This bit controls the data and byte

enable steering logic that was implemented in the

pci_mt64

and

pci_t64

MegaCore functions

before version 2.0.0. When this bit is set to 0, only

the

l_dato[31..0]

and

l_beno[3..0]

buses will contain valid data during a 32-bit

master read (when a 64-bit transaction was

requested) or a 32-bit target write. Setting this bit

to 1 will implement the steering logic, providing

100% backward compatible operation with

versions prior to 2.0.0. If starting a new design,

Altera recommends adding the data steering logic

in the local side application for lower logic

utilization and better overall performance.

Table 2–2. Bit Definition of the ENABLE_BITS Parameter (Part 3 of 5)

Bit

Number

Bit Name

Default

Value

Definition