Altera PCI Compiler User Manual

Page 226

4–16

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Local Reference Design

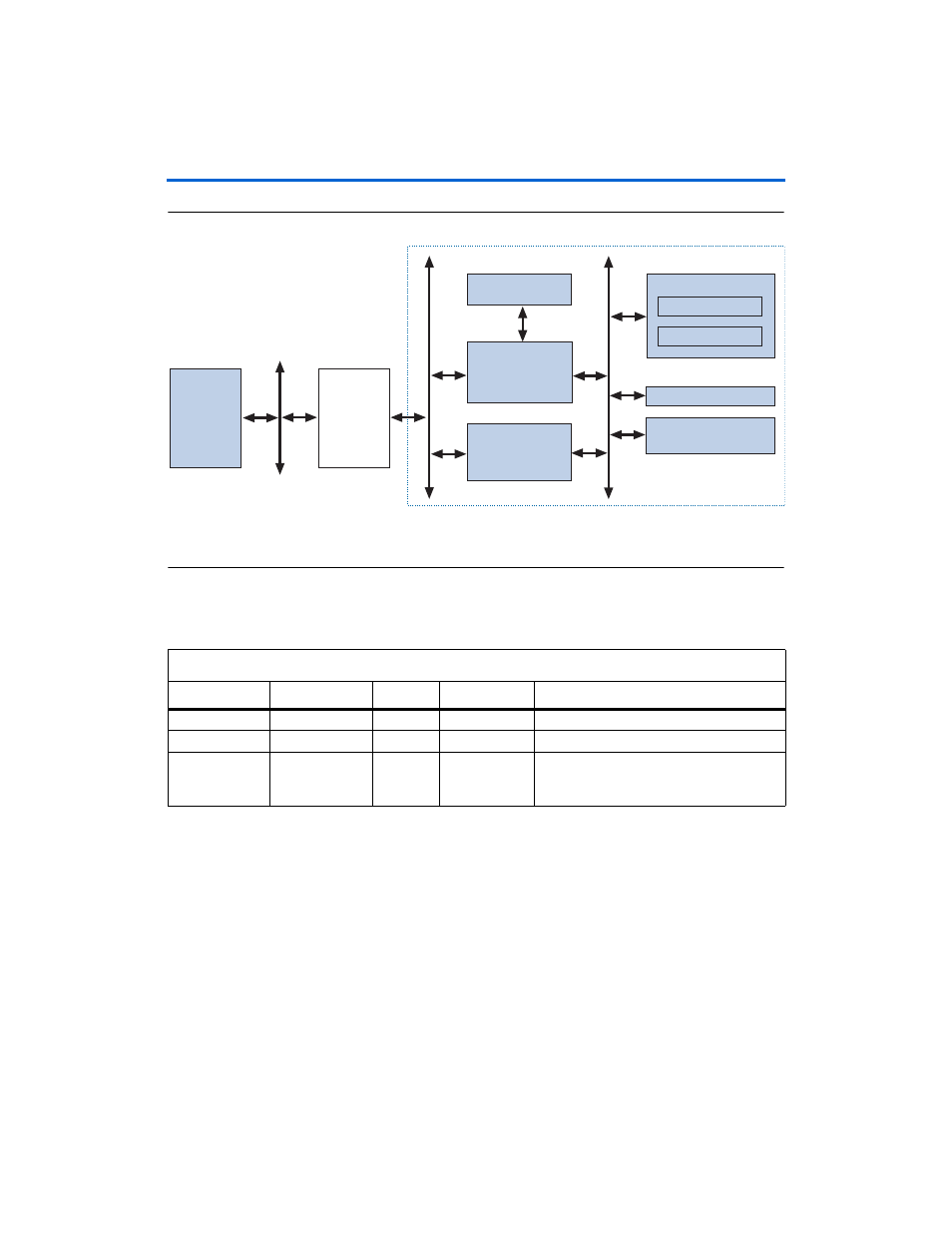

Figure 4–3. Local Reference Design

(1)

The DMA Engine, lm_lastn and local master blocks are not applicable for the pci_t32 and pci_t64 local reference

designs.

shows the memory map of the Altera PCI MegaCore function

required to use the local reference design.

The reference design has the following elements:

■

Local target

■

DMA engine

■

Local master

■

lm_lastn

generator

■

Prefetch

■

LPM RAM

Local

Target

Prefetch

LPM RAM

Altera PCI

MegaCore

Function

Testbench

Modules

Local Reference Design

PCI Bus

dma_sa

dma_bc_la

DMA Engine

(1)

lm_lastn

(1)

Local

Master

(1)

Table 4–8. Memory Map

Memory Region

Mapping

Block size Address Offset

Description

BAR0

Memory Mapped 1 KByte

000-3FF

Maps the LPM_RAM function.

BAR1

I/O Mapped

16 Bytes

0-F

Maps the I/O register.

BAR2

Memory Mapped 1 KByte

000-3FF

Maps the

trg_termination

register and

DMA engine registers. Only the lower 24

Bytes of the address space are used.