Additional options, Speed – Altera PCI Compiler User Manual

Page 349

Altera Corporation

User Guide Version 11.1

A–3

October 2011

PCI Compiler

f

For more recommendations on reducing SSN in your design, refer to

.

Additional

Options

The command syntax description for the add_pci_constraints

command is the following:

add_pci_constraints

[-speed "66" | "33"] [-no_compile]

[-no_pinouts][-pin_prefix <instance name_>]

[-pin_suffix <_instance name>] -help

r

These options for the add_pci_constraints command are described

in the following sections.

-speed

The default value for this option is the maximum speed supported by the

targeted device family.

shows the device speed grades required for 33-MHz or

66-MHz operation, and the default speed selected by the PCI constraint

file for each supported device family.

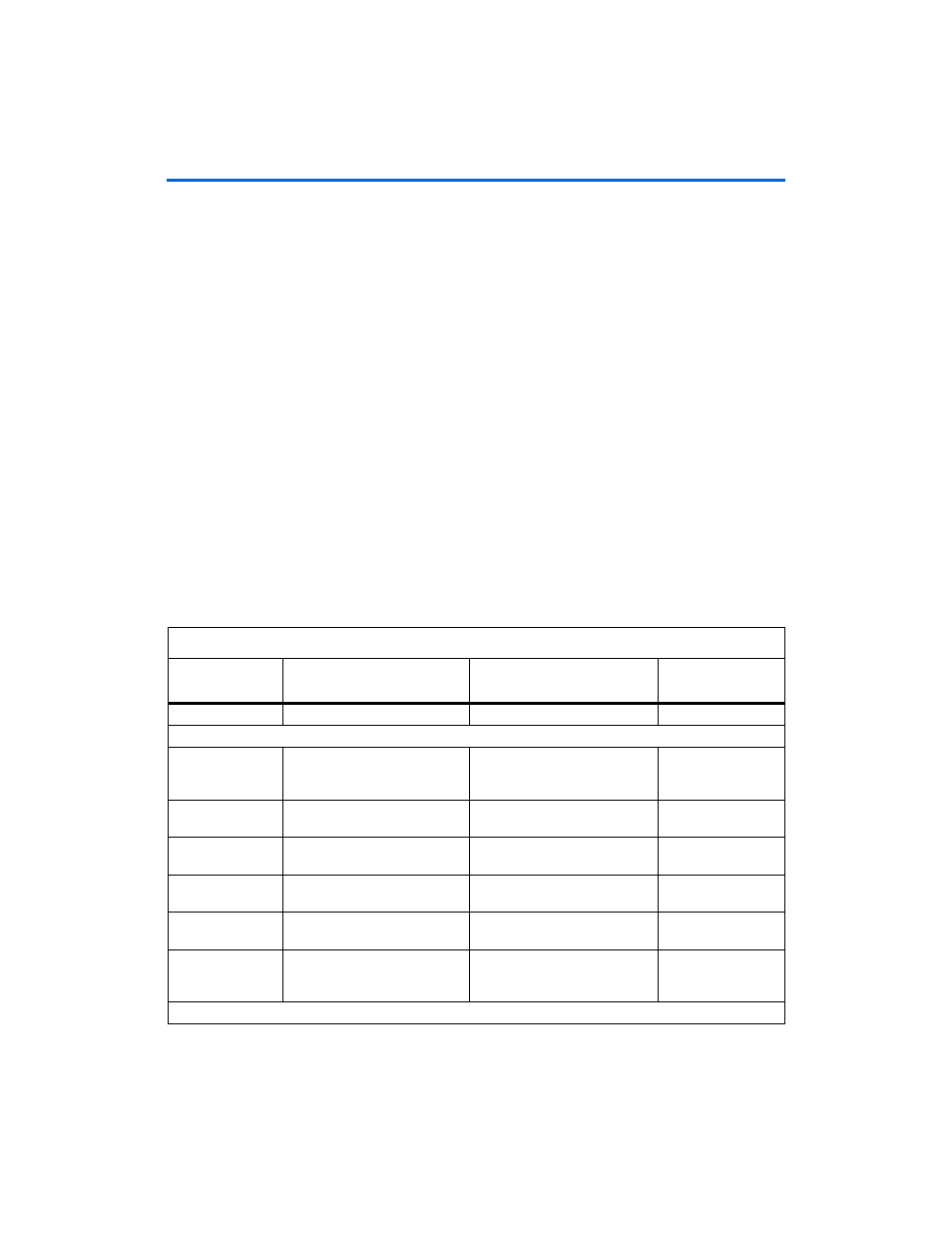

Table A–1. Default -speed Value for Supported Device Families

Device Family

Speed Grade Required for

66 MHz operation

Speed Grade Required for

33 MHz Operation

Default PCI Bus

Speed

Arria GX

-6

-6

66 MHz

Arria II GX:

EP2AGX125DF25

EP2AGX125EF29

EP2AGX125EF35

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

EP2AGX190EF29

EP2AGX190FF35

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

EP2AGX260EF29

EP2AGX260FF35

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

EP2AGX45DF25

EP2AGX45DF29

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

EP2AGX65DF25

EP2AGX65DF29

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

EP2AGX95DF25

EP2AGX95EF29

EP2AGX95EF35

-3, -4, -5, -6

-3, -4, -5, -6

66 MHz

Arria II GZ: