Altera PCI Compiler User Manual

Page 92

3–18

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

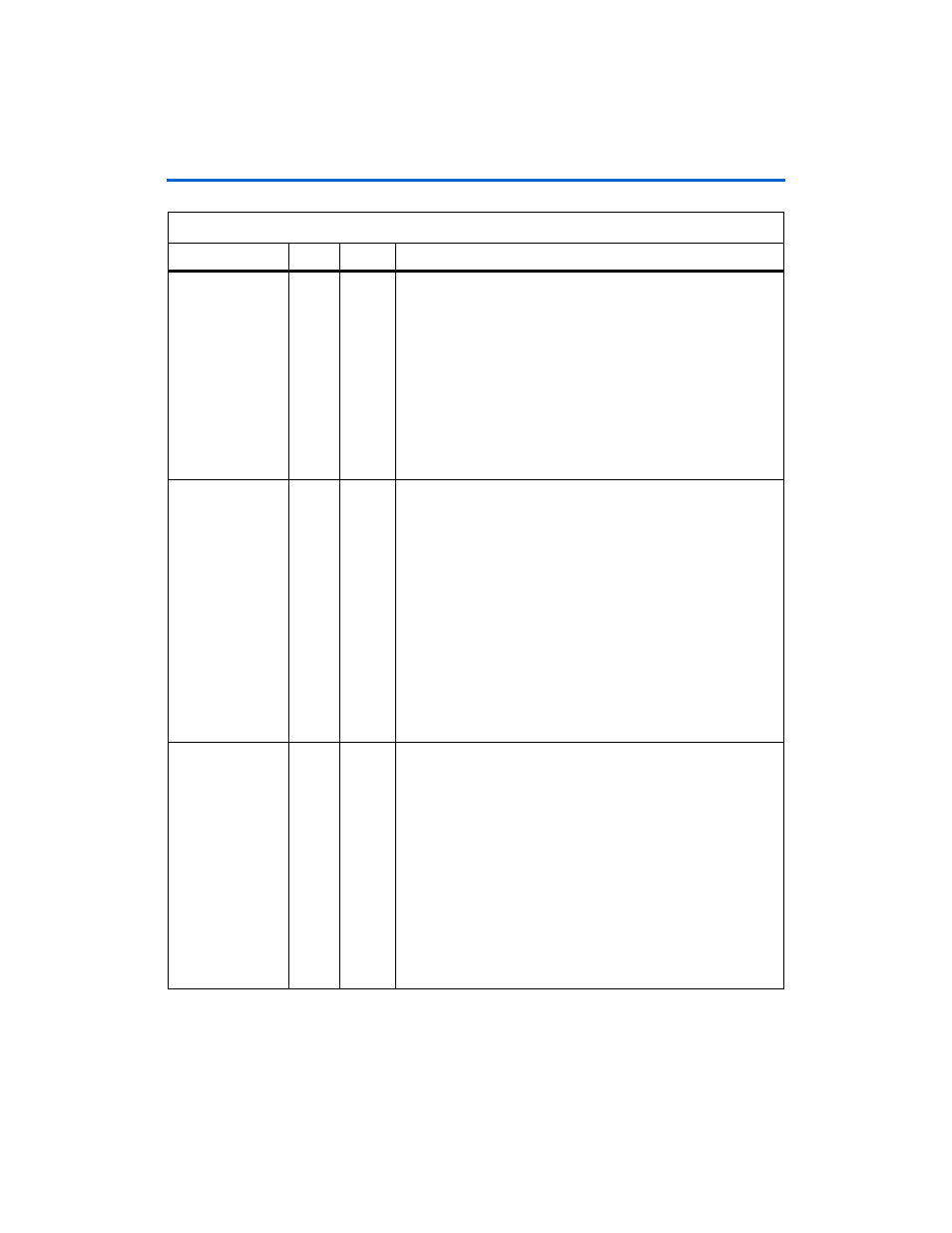

PCI Bus Signals

l_adro[63..0]

Output

–

Local address output. The l_adro[63..0] bus is driven by the PCI

MegaCore functions during target transactions. The pci_mt32 and

pci_t32 functions only implement l_adro[31..0]. During dual address

transactions in the pci_mt64 and pci_t64 MegaCore functions, the

l_adro[63..32] bus is driven with a valid address. DAC is indicated by

the assertion of lt_tsr[11]. For more information on the local target

status signals, refer to

The falling edge of lt_framen indicates a valid l_adro[63..0]. The PCI

address is held at the local side as long as possible and should be

assumed invalid at the end of the target transaction on the PCI bus.

The end of the target transaction is indicated by lt_tsr[8] (targ_access)

being deasserted.

l_dato[63..0]

Output

–

Local data output. The

l_dato[63..0]

bus is driven active during

PCI bus-initiated target write transactions or local side-initiated master

read transactions. The functionality of this bus changes depending on

the function you are using and the transaction being considered. The

pci_mt32

and

pci_t32

functions implement only

l_dato[31..0]

. The operation in the

pci_mt64

and

pci_t64

MegaCore functions is dependent on the type of transaction being

considered. During 64-bit target write transactions and master read

transactions, the data is transferred on the entire

l_dato[63..0]

bus. During 32-bit master read transactions, the data is only

transferred on

l_dato[31..0]

. During 32-bit target write

transactions, the data is also only transferred on

l_dato[31..0]

;

however, depending on the transaction address, the

pci_mt64

or

pci_t64

MegaCore function either asserts

l_ldat_ackn

or

l_hdat_ackn

to indicate whether the address for the current data

word is a

QWORD

boundary (

ad[2..0] = B"000"

) or not.

l_beno[7..0]

Output

–

Local byte enable output. The

l_beno[7..0]

bus is driven by the

PCI function during target transactions. This bus holds the byte enable

value during data transfers. The functionality of this bus is different

depending on the function being used and the transaction being

considered. The

pci_mt32

and

pci_t32

functions implement only

l_beno[3..0]

. The operation in the

pci_mt64

and

pci_t64

MegaCore functions is dependent on the type of transaction being

considered. During 64-bit target write transactions, the byte enables

are transferred on the entire

l_beno[7..0]

bus. During 32-bit

target write transactions, the byte enables are transferred on the

l_beno[3..0]

bus and, depending on the transaction address, the

pci_mt64

or

pci_t64

MegaCore function either asserts

l_ldat_ackn

or

l_hdat_ackn

to indicate whether the address

for the current byte enables is at a

QWORD

boundary (

ad[2..0] =

B"000"

) or not.

Table 3–6. PCI Local Address, Data, Command & Byte Enable Signals (Part 2 of 3)

Name

Type

Polarity

Description