Master simulation files – Altera PCI Compiler User Manual

Page 47

Altera Corporation

User Guide Version 11.1

1–13

October 2011

PCI Compiler

Getting Started

Master Simulation Files

describes the Quartus II simulation files included in the

<path>\pci_compiler\megawizard_flow\qexamples\

pci_mt64\sim\master

directory.

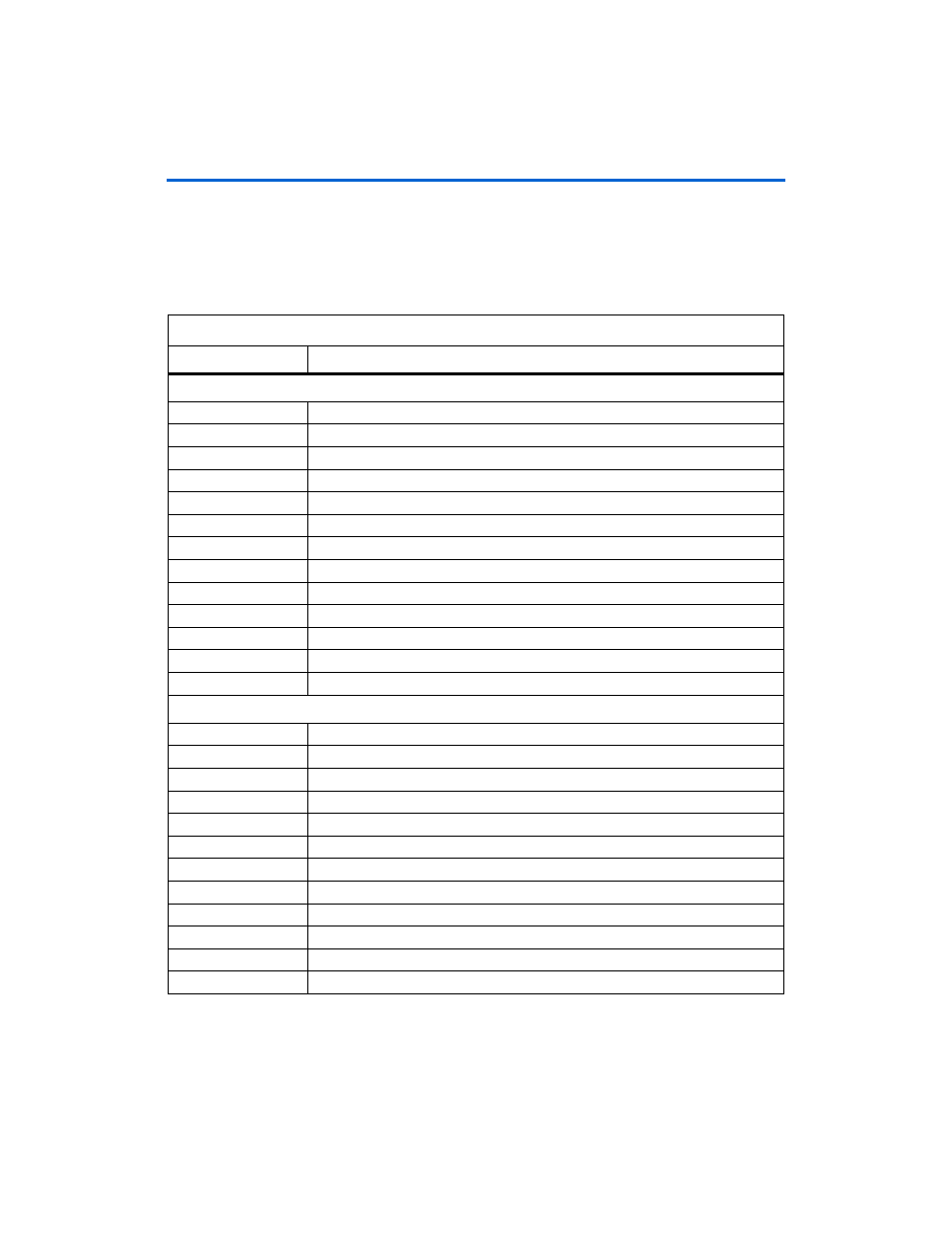

Table 1–2. pci_mt64 Master Simulation Files

Simulation File Name

Description

Master Read

mmbr64

Memory Burst Read, 64-Bit PCI, 64-Bit Local

mmbr32_64

Memory Burst Read, 32-Bit PCI, 64-Bit Local

mmbr32_32

Memory Burst Read, 32-Bit PCI, 32-Bit Local

mmsr64

Memory Single-Cycle, 64-Bit PCI, 64-Bit Local

mmsr32_32

Memory Single-Cycle, 32-Bit PCI, 32-Bit Local

mmbr64_mabrt

Master Abort, 64-Bit PCI, 64-Bit Local

mmbr64_tabrt

Target Abort Response, 64-Bit PCI, 64-Bit Local

mmbr64_tdisc_wd

Target Disconnect with Data Response, 64-Bit PCI, 64-Bit Local

mmbr64_tdisc_wod

Target Disconnect without Data Response, 64-Bit PCI, 64-Bit Local

mmbr64_tret

Target Retry Response, 64-Bit PCI, 64-Bit Local

mmbr64_lte

Latency Timer Expires, 64-Bit PCI, 64-Bit Local

mior

I/O Read

mcfgr

Configuration Read

Master Write

mmbw64

Memory Burst Write, 64-Bit PCI, 64-Bit Local

mmbw32_64

Memory Burst Write, 32-Bit PCI, 64-Bit Local

mmbw32_32

Memory Burst Write, 32-Bit PCI, 64-Bit Local

mmsw32_32

Memory Single-Cycle, 32-Bit PCI, 32-Bit Local

mmbw64_mabrt

Master Abort, 64-Bit PCI, 64-Bit Local

mmbw64_tabrt

Target Abort Response, 64-Bit PCI, 64-Bit Local

mmbw64_tdisc_wd

Target Disconnect with Data Response, 64-Bit PCI, 64-Bit Local

mmbw64_tdisc_wod

Target Disconnect without Data Response, 64-Bit PCI, 64-Bit Local

mmbw64_tret

Target Retry Response, 64-Bit PCI, 64-Bit Local

mmbw64_lte

Latency Timer Expires, 64-Bit PCI, 64-Bit Local

miow

I/O Write

mcfgw

Configuration Write