Pci compiler with sopc builder flow – Altera PCI Compiler User Manual

Page 25

Altera Corporation

User Guide Version 11.1

13

October 2011

About PCI Compiler

shows PCI MegaCore function resource utilization and

performance data for Cyclone II devices.

shows PCI MegaCore function resource utilization and

performance for MAX II devices.

PCI Compiler with SOPC Builder Flow

The speed and resource utilization estimates are for the supported

devices when operating in the PCI Target-Only, PCI Master/Target, and

PCI Host-Bridge device modes for each of the application-specific

performance settings.

1

Performance results will vary depending on the user-specified

parameters that are built into the system module.

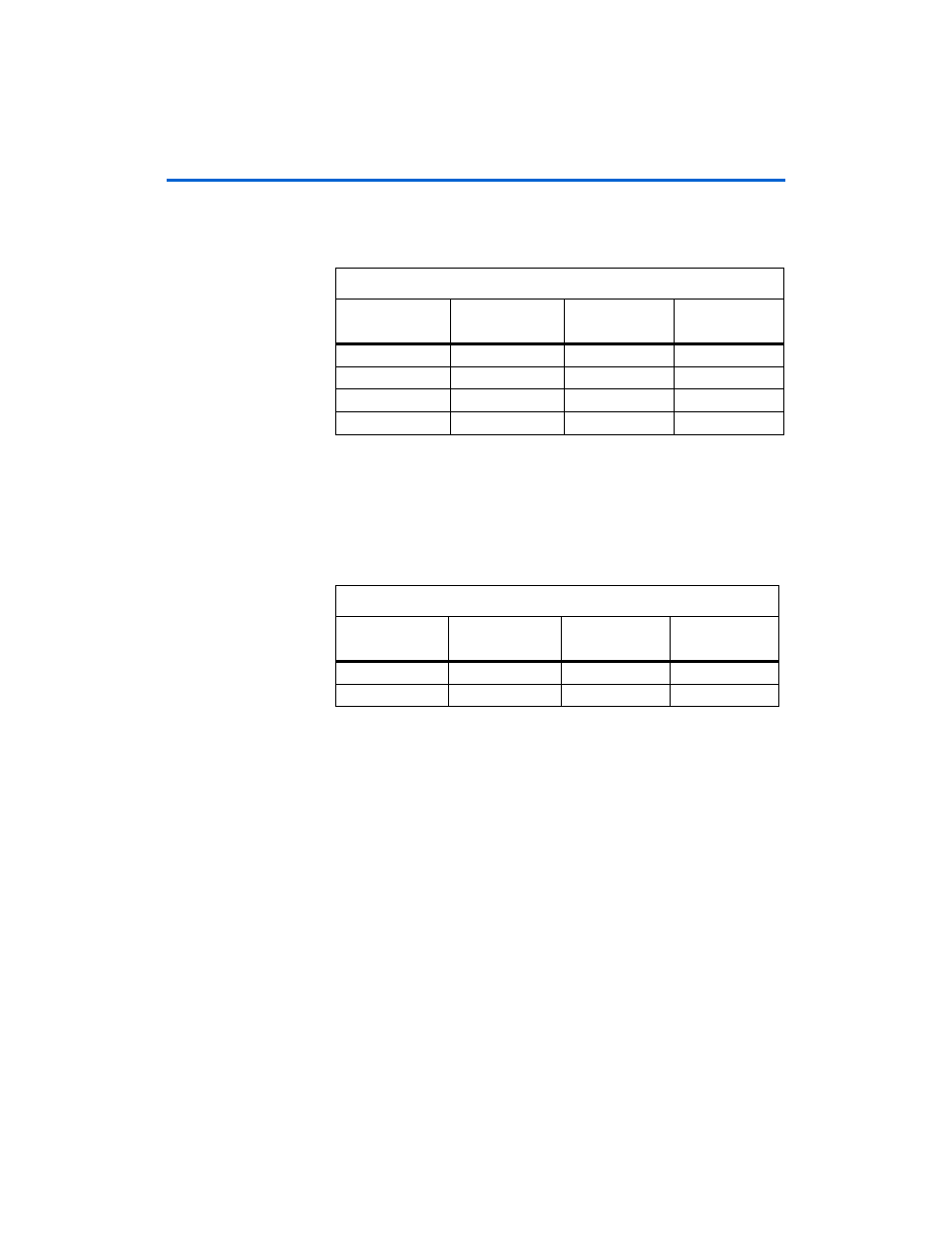

Table 6. PCI MegaCore Function Performance in Cyclone II Devices

PCI Function

Logic Elements

(LEs)

I/O Pins

f

MAX

(MHz)

pci_mt64

1,219

89

> 67

pci_t64

778

87

> 67

pci_mt32

847

50

> 67

pci_t32

504

48

> 67

Note to

(1)

This data was obtained by compiling each of the PCI MegaCore functions

(parameterized to use one BAR that reserves 1 MByte of memory) in the

Cyclone II EP2C35F672C7 device.

Table 7. PCI MegaCore Function Performance in MAX II Devices

PCI Function

Logic Elements

(LEs)

I/O Pins

f

MAX

(MHz)

pci_mt32

789

50

> 67

pci_t32

455

48

> 67

:

(1)

This data was obtained by compiling each of the PCI MegaCore functions

(parameterized to use one BAR that reserves 1 MByte of memory) in the MAX II

EPM2210F324C3 device.

(2)

pci_mt64

and pci_t64 MegaCore functions are not supported in MAX II

devices.