Synthesis & compilation instructions – Altera PCI Compiler User Manual

Page 54

1–20

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Using the Reference Designs

Refer to

the pci_mt32 MegaCore Function Reference Design

Directory Structure for more details regarding the directory structure.

Synthesis & Compilation Instructions

To compile the

pci_mt32

MegaCore Function Reference Design in the

Quartus II software, perform the following steps:

1.

Create a new project in the Quartus II software, specifying

<path>/pci_compiler/megawizard_flow/

ref_designs/pci_mt32/vhdl/chip_top.vhd

as the top-level

design file.

2.

Add the following directories as user libraries in the Quartus II

software:

<path>/pci_compiler/lib

<path>/pci_compiler/megawizard_flow/

ref_designs/pci_mt32/vhdl/chip_top

<path>/pci_compiler/megawizard_flow

/ref_designs/pci_mt32/vhdl/pci_local

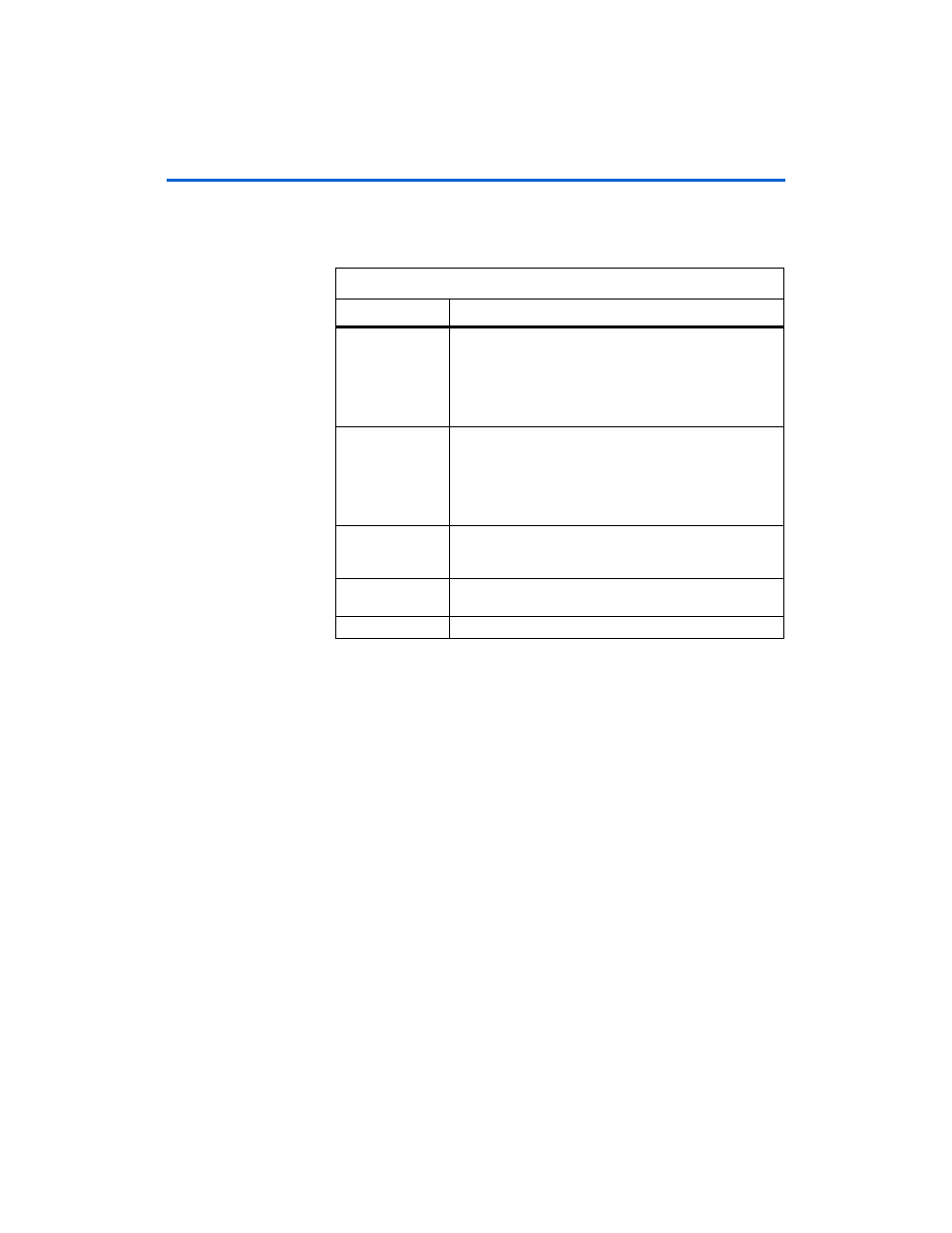

Table 1–6. Directory Structure of pci_mt32 MegaCore Reference Design

Directory Name

Description

chip_top

This directory contains a top-level design file that

instantiates the following modules:

●

pci_mt32 MegaCore function variation file

●

Local interface logic

●

SDR SDRAM interface

●

SDR SDRAM controller

pci_top

This directory contains a pci_mt32 MegaCore function top-

level wrapper file. This wrapper file was generated using IP

Toolbench with the following parameters selected using the

Parameterize - PCI Compiler Wizard:

●

BAR0 reserves 1MB of memory space

●

BAR1 reserves 32MB of memory space

pci_local

This directory contains local interface logic files. For more

information on these files, refer to FS 12: pci_mt32

MegaCore Function Reference Design.

sdr_intf

This directory contains files for the interface logic between

the PCI local interface logic and the SDR SDRAM controller.

sdr_cntrl

This directory contains files for the SDR SDRAM controller.