Altera PCI Compiler User Manual

Page 257

Altera Corporation

User Guide Version 11.1

6–7

October 2011

Parameter Settings

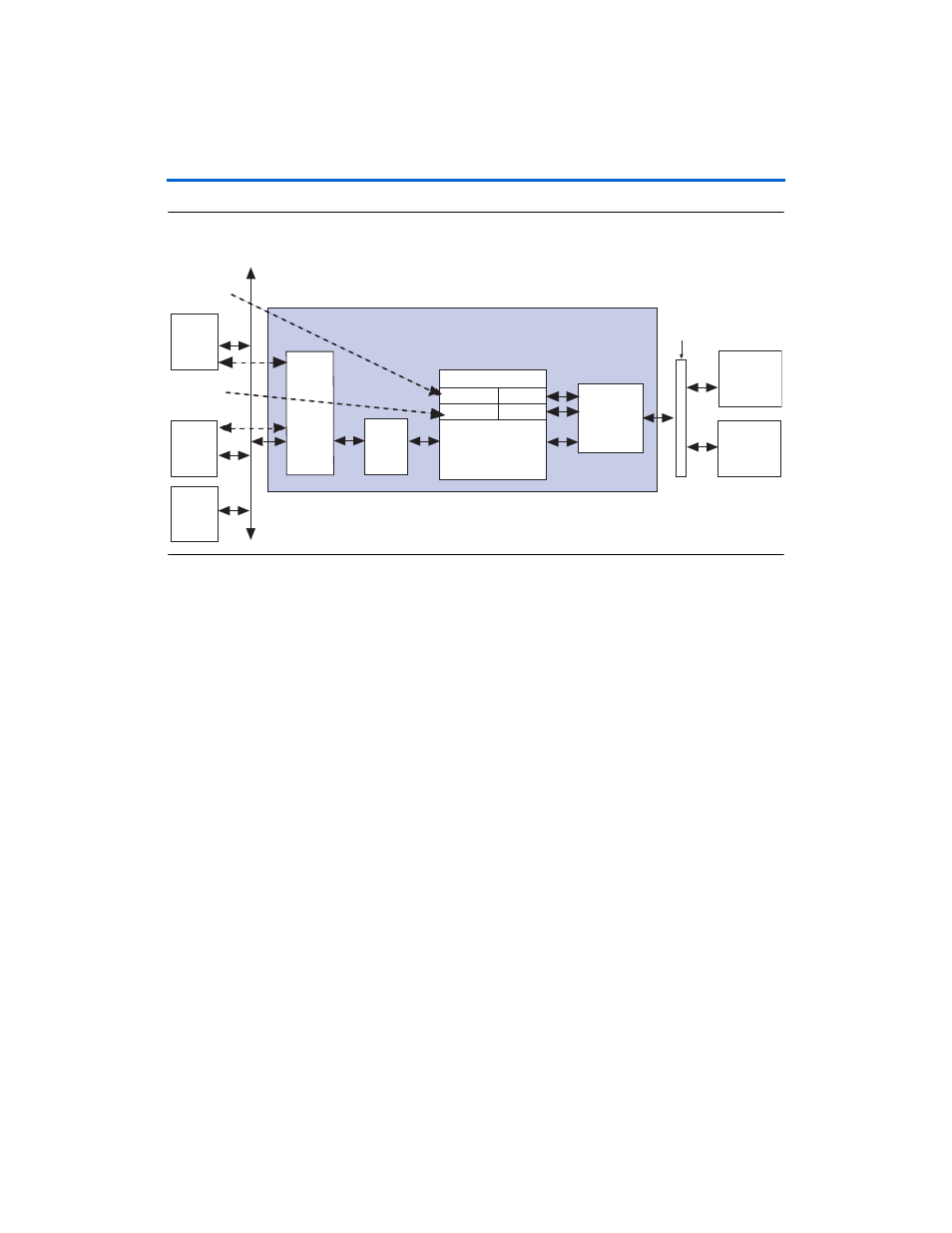

Figure 6–1. PCI-Avalon Bridge Burst Transfer with Multiple Pending Reads

In contrast, the same two reads will complete in the following sequence if

multiple pending read transactions are not allowed:

1.

PCI Agent 0 requests a read transaction (R0) to address 0x4. The

PCI-Avalon bridge issues a PCI retry, stores the necessary

information from the R0 transaction, and begins to retrieve the

requested data from the Avalon-MM peripheral.

2.

Before the R0 transaction completes, PCI Agent 1 requests a read

transaction (R1) to address 0xC. Because the PCI-Avalon bridge is

currently servicing the R0 transaction, it simply issues a retry in

response to R1 and continues to retrieve the data for R0. In this case,

no information about R1 is stored in the PCI-Avalon bridge.

3.

At some point the data for R0 is returned by the Avalon-MM

peripheral. Meanwhile, all read transactions are automatically

retried by the PCI-Avalon bridge.

4.

PCI Agent 0 reissues the R0 transaction, and the PCI-Avalon bridge

provides the requested data and completes the R0 transaction.

5.

At a later time, PCI Agent 1 attempts R1 again. The PCI-Avalon

bridge issues a PCI retry, stores the necessary information from the

R1 transaction, and begins to retrieve the requested data the from

Avalon-MM peripheral.

PCI-Avalon Bridge

Burst Transfers with Concurrent Transactions

PCI

Target

Controller

Pending Read Buffer

PCI

MegaCore

Function

Prefectable

Avalon

Master

Avalon

Slave

Peripheral #2

PCI

Master/

Target

Agent 0

PCI

Bus

Arbiter

PCI

Bus

Agent 0

Read

Address 0x4

Agent 1

Read

Address 0xC

PCI

Master/

Target

Agent 1

Avalon

Slave

Peripheral #1

System

Interconnect

Fabric

Rd Addr 0x4

Rd Addr 0xC

Rd Data

Rd Data

Prefetchable

Bridge

Logic

PCI-Avalon Bridge