Altera PCI Compiler User Manual

Page 316

7–48

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Control & Status Registers

Because all accesses come from Avalon-MM (requests from the PCI bus

are routed through Avalon-MM), there is no hardware controlling which

processors access which regions. However, enforcement via processor

software is designed to be straightforward.

describes the four

sub-regions.

The data returned to a read issued to any undefined address in this range

is unpredictable.

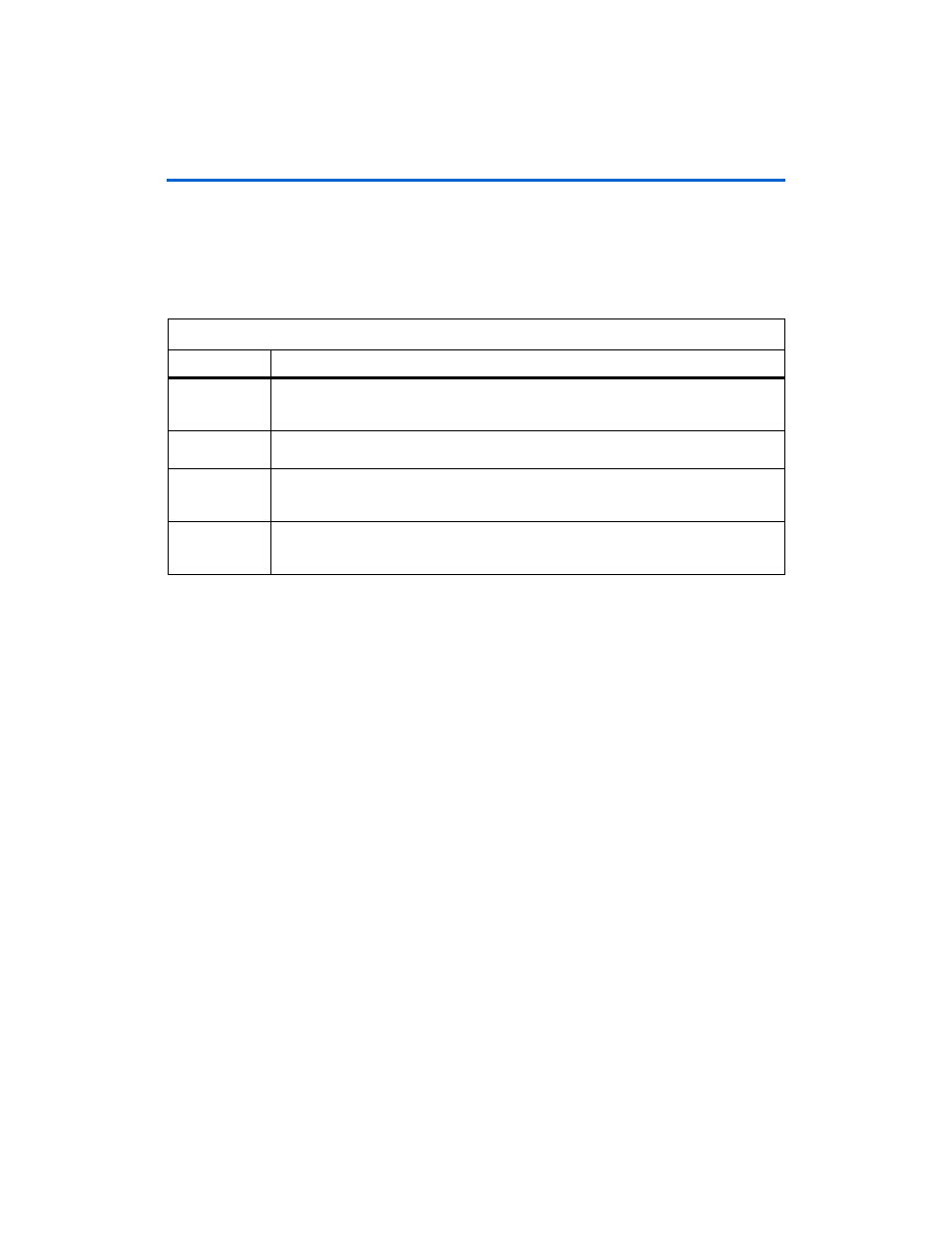

Table 7–16. Control and Status Register Address Spaces

Address Range

Address Space Usage

0x0000-0x0FFF

Registers typically intended for access by PCI processors only. This includes PCI interrupt

enable controls, write access to the PCI-to-Avalon mailbox registers, and read access to

Avalon-to-PCI mailbox registers.

0x1000-0x1FFF

Avalon-to-PCI address translation tables. Depending on the system design, these may be

accessed by PCI processors, Avalon processors, or both.

0x2000-0x2FFF

Read only registers that reflect various configuration parameters of the implementation.

Depending on the system design these may be accessed by PCI processors, Avalon

processors, or both.

0x3000-0x3FFF

Registers typically intended for access by Avalon processors only. This includes Avalon-MM

interrupt enable controls, I/O and configuration request control registers, write access to the

Avalon-to-PCI mailbox registers, and read access to PCI-to-Avalon mailbox registers.