Altera 100G Interlaken MegaCore Function User Manual

Page 103

Performance and Fmax Requirements for 100G

Ethernet Traffic

A

2015.05.04

UG-01128

To achieve 100G Ethernet line rates through the application interface of your 100G Interlaken IP core,

you must run the transmit side and receiver side user interface clocks

tx_usr_clk

and

rx_usr_clk

at the

following minimum required operating frequency:

• 300 MHz in single segment mode and in 24 lane variations

(2)

• 225 MHz in 12 lane variations in dual segment mode

The following discussion describes the packet rate calculation that supports this requirement.

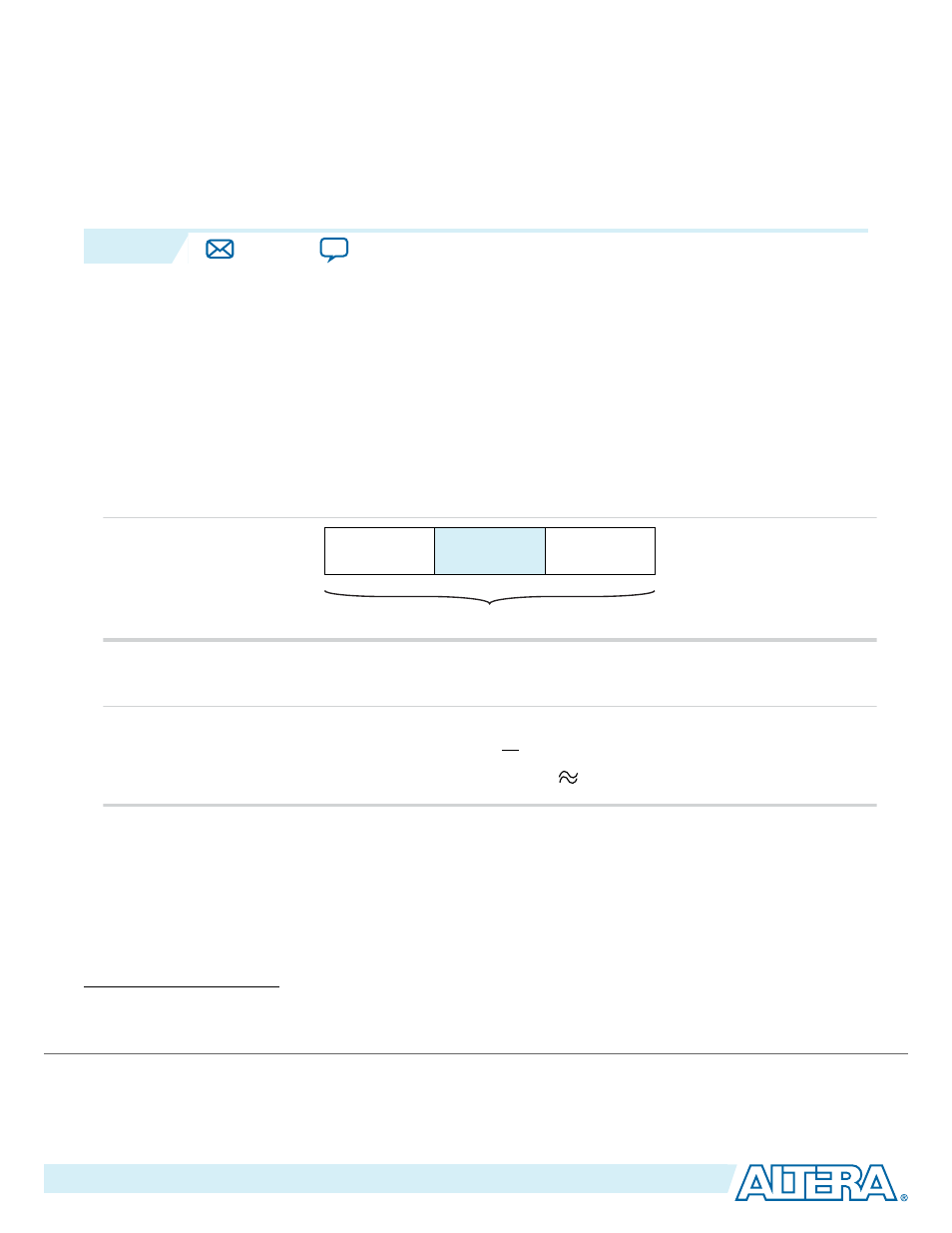

Figure A-1: Interlaken Ethernet Packet

To transmit a minimum size (64-byte) Ethernet packet, the Interlaken link transmitter must send 672 bits

of data.

Preamble

8 Bytes

Minimum Packet

64 Bytes

Interpacket Gap

12 Bytes

672 Bits

To support an Ethernet line rate of 100Gb/s, the Interlaken link must process 1000 bits in 10ns. The

following calculation derives the required clock frequency.

.

150 million packets/sec

100 x 1,000,000,000 bits/sec

.

672 = 148.8 million packets/sec

This packet rate requires that the user interface handle one packet per cycle if the operating clock runs at

150 MHz, or one packet per two cycles if the operating clock runs at 300 MHz.

In dual segment mode, because the final cycle of one packet can overlap with the initial cycle of another

packet, the operating clock frequency requirements are derived from the average number of cycles

required for a single packet in back-to-back traffic. The calculations that follow show that the minimum

operating clock frequency in dual segment mode is 225 MHz.

(2)

The restriction to a minimum of 300 MHz in dual segment mode in 24 lane variations is an artifact of the

clocking scheme in this IP core.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134