Altera 100G Interlaken MegaCore Function User Manual

Page 77

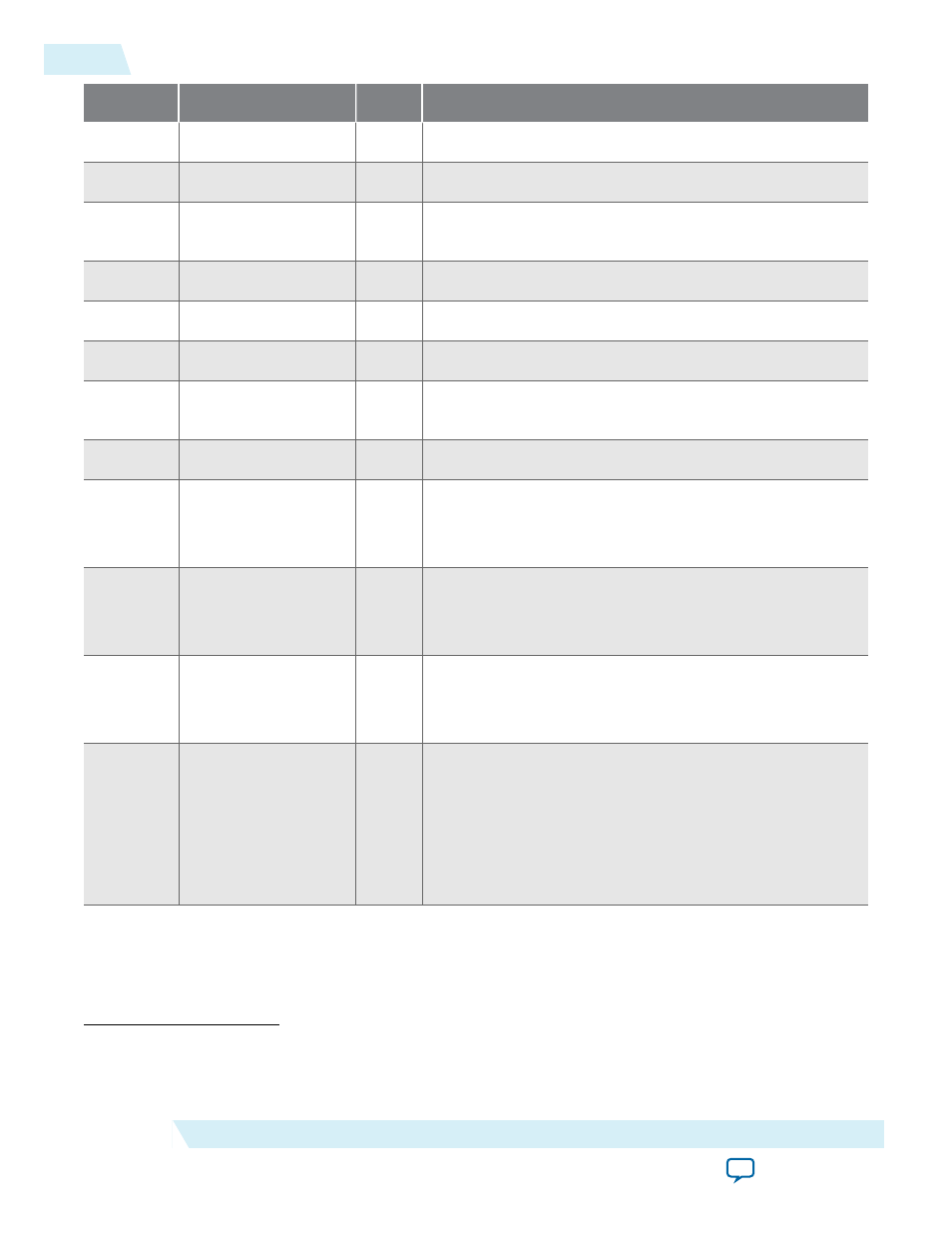

Offset

Name

R/W

Description

9'h4

TX_EMPTY

RO

[NUM_LANES–1:0] – Transmit FIFO status (empty)

9'h5

TX_FULL

RO

[NUM_LANES–1:0] – Transmit FIFO status (full)

9'h6

TX_PEMPTY

RO

[NUM_LANES–1:0] – Transmit FIFO status (partially

empty)

9'h7

TX_PFULL

RO

[NUM_LANES–1:0] – Transmit FIFO status (partially full)

9'h8

RX_EMPTY

RO

[NUM_LANES–1:0] – Receive FIFO status (empty)

9'h9

RX_FULL

RO

[NUM_LANES–1:0] – Receive FIFO status (full)

9'hA

RX_PEMPTY

RO

[NUM_LANES–1:0] – Receive FIFO status (partially

empty)

9'hB

RX_PFULL

RO

[NUM_LANES–1:0] – Receive FIFO status (partially full)

9'hC

REF_KHZ

(1)

RO

PLL reference clock frequency (kHz)

If you turn off Include diagnostic features, this register is

not available.

9'hD

RX_KHZ

(1)

RO

RX recovered clock frequency (kHz)

If you turn off Include diagnostic features, this register is

not available.

9'hE

TX_KHZ

(1)

RO

TX serial clock frequency (kHz)

If you turn off Include diagnostic features, this register is

not available.

9'hF

LANE_PROFILE

RO

[NUM_LANES–1:0] – Mask delineating the transceivers

this IP core uses on the device. For example, if the FPGA

has 24 lanes on one side of the device and the IP core uses

the bottom twelve transceivers, the mask would be

24'b000000_000000_111111_111111..

This register is not available in IP core variations that target

an Arria 10 device.

(1)

Altera recommends that you use this register only during hardware operation. During simulation, you

should not rely on the value in this register, because the amount of simulation time required for the IP core

to provide consistent values in the REF_KHZ, RX_KHZ, and TX_KHZ registers is too long.

6-2

100G Interlaken IP Core Register Map

UG-01128

2015.05.04

Altera Corporation

100G Interlaken IP Core Register Map