Altera 100G Interlaken MegaCore Function User Manual

Page 55

application can rely on the fact that if

irx_err

is not asserted and

irx_eopbits

has a value other than

4'b0001, the packet is not errored.

For CRC24 errors, you should use the

crc24_err

status signal, rather than relying on the

irx_err

signal,

in the following situations:

• If you monitor the link when only Idle control words are being received (no data is flowing), you

should monitor the real time status signal

crc24_err

.

• If you maintain a count of CRC24 errors, you should monitor the number of times that the real time

status signal

crc24_err

is asserted.

If you turn off Include advanced error reporting and handling,

irx_err

behaves identically to the

crc24_err

signal.

Related Information

Include Advanced Error Reporting and Handling

on page 3-3

100G Interlaken IP Core Receiver Side Example With Errors and In-Band Calendar Bits

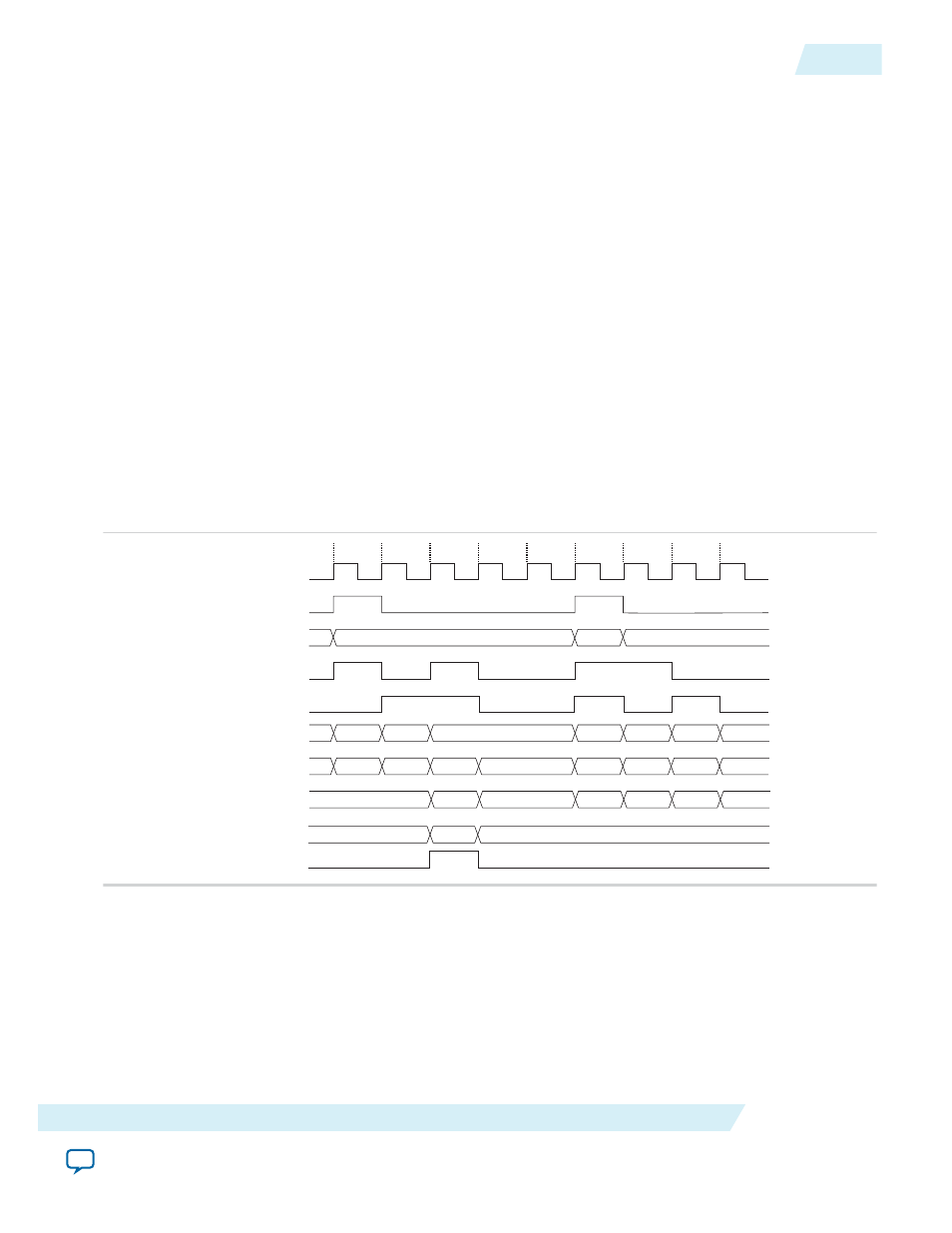

Figure 4-12: 100G Interlaken IP Core Receiver Side Single Segment Example With irx_err Errors

This example illustrates the expected behavior of the 100G Interlaken IP core application interface receive

signals during a packet transfer in single segment mode with CRC or other errors. In the example, the

errored packet transfer is followed by two idle cycles and a non-errored packet transfer.

rx_usr_clk

irx_sop[1]

irx_chan

irx_sob[1]

irx_eob

irx_dout_words

irx_num_valid[7:4]

irx_eopbits

irx_calendar

irx_err

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7 Cycle 8 Cycle 9

8’h2

8’h3

d1

d2

d3

d4

d5

d6

4’b1000 4’b1000

4’b1000

4’b0111 4’b0000

4’b1000 4’b0010

4’b0000

4’b0000

4’b1011

4’b1011

64’hffff_ffff_ffff_ffff

///////////64’h1111_2222_3333_4444

This figure illustrates the attempted transfer of a 179-byte packet on the RX user data transfer interface to

channel 2, after the 100G Interlaken IP Core receives the packet on the Interlaken link and detects

corruption. Following the errored packet, the IP core transfers an uncorrupted packet to channel 3.

In cycle 1, the 100G Interlaken IP Core asserts

irx_sop[1]

when data is ready on

irx_dout_words

.

When the 100G Interlaken IP Core asserts

irx_sop[1]

, it also asserts the correct value on

irx_chan

to

tell the application the data channel destination of the data. In this example, the value 2 on

irx_chan

tells

the application that the data should be sent to channel number 2.

During the SOP cycle (labeled with data value d1) and the cycle that follows the SOP cycle (labeled with

data value d2), the 100G Interlaken IP Core holds the value of

irx_num_valid[7:4]

at 4'b1000. In the

UG-01128

2015.05.04

100G Interlaken IP Core Receiver Side Example With Errors and In-Band Calendar Bits

4-25

Functional Description

Altera Corporation