Interleaved and packet modes, Interleaved and packet modes -7 – Altera 100G Interlaken MegaCore Function User Manual

Page 37

•

For more information about the Altera reset controller that is included in Arria 10 variations of the

100G Interlaken IP core, refer to the Using the Altera Transceiver PHY Reset Controller section of this

user guide.

IP Core Reset Sequence with the Reconfiguration Controller

If your 100G Interlaken IP core targets an Arria V device or a Stratix V device, you must connect the

100G Interlaken IP core to an Altera Reconfiguration Controller. At power up, the Reconfiguration

Controller configures the transceivers. After power up, upon completion of the transceiver configuration

process, the Reconfiguration Controller returns control of the reset to your application. You must wait

until the Reconfiguration Controller completes configuration of the transceivers before you assert the

reset_n

signal.

The Reconfiguration Controller indicates the end of the configuration cycle by deasserting the

reconfig_busy

signal. After

reconfig_busy

is deasserted, you can assert

reset_n

. Altera recommends

that you hold the

reset_n

signal low for at least the duration of two

mm_clk

cycles, to ensure the reset

sequence proceeds correctly.

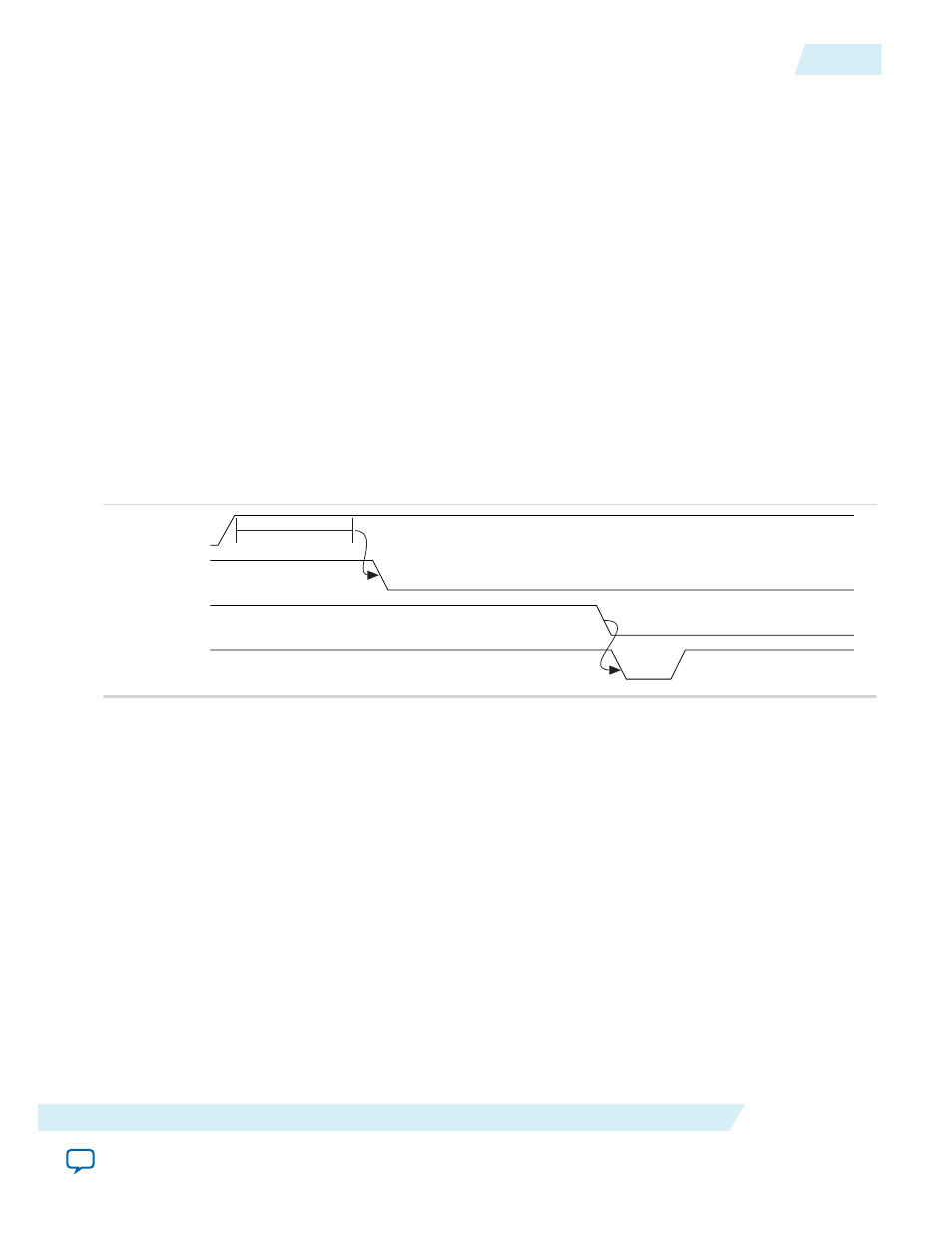

Figure 4-3: Reset Sequence With the Reconfiguration Controller

Indicates when you can safely assert the

reset_n

signal of the 100G Interlaken MegaCore IP core.

mgmt_clk_locked

mgmt_rst_reset

reconfig_busy

reset_n

(*)

You must wait at least 2

23

mm_clk

cycles (or 2

9

mm_clk

cycles in simulation) after the mgmt_clk locks

before you deassert the

mgmt_rst_reset

input signal to the reconfiguration controller.

Related Information

•

For more information about the Altera Reconfiguration Controller.

Interleaved and Packet Modes

You can configure the 100G Interlaken IP core to accept interleaved data transfers from the application

on the TX user data transfer interface, or to not accept interleaved data transfers on this interface. If the IP

core can accept interleaved data transfers, it is in Interleaved mode, sometimes also called Segmented

mode. If the IP core does not accept interleaved data transfers, it is in Packet mode. The value you specify

for the Transfer mode selection parameter in the 100G Interlaken parameter editor determines the IP

core transmit mode.

UG-01128

2015.05.04

IP Core Reset Sequence with the Reconfiguration Controller

4-7

Functional Description

Altera Corporation