Altera 100G Interlaken MegaCore Function User Manual

Page 13

a. Click Finish. The Generation dialog box appears.

b. Click Exit. The parameter editor adds the top-level

.qsys

file to the current project automatically. If

you are prompted to manually add the

.qsys

file to the project, click Project > Add/Remove Files in

Project to add the file.

6. After generating and instantiating your IP variation, make appropriate pin assignments to connect

ports.

If you specify the Verilog HDL for your IP core files, the Quartus II software creates the demonstration

testbench and example design when it generates the IP core.

Related Information

100G Interlaken IP Core Parameter Settings

Details about the parameters available in the 100G Interlaken parameter editor.

Files Generated for Arria V GZ and Stratix V Variations

The Quartus II software generates multiple files during generation of your 100G Interlaken IP core Arria

V GZ or Stratix V variation.

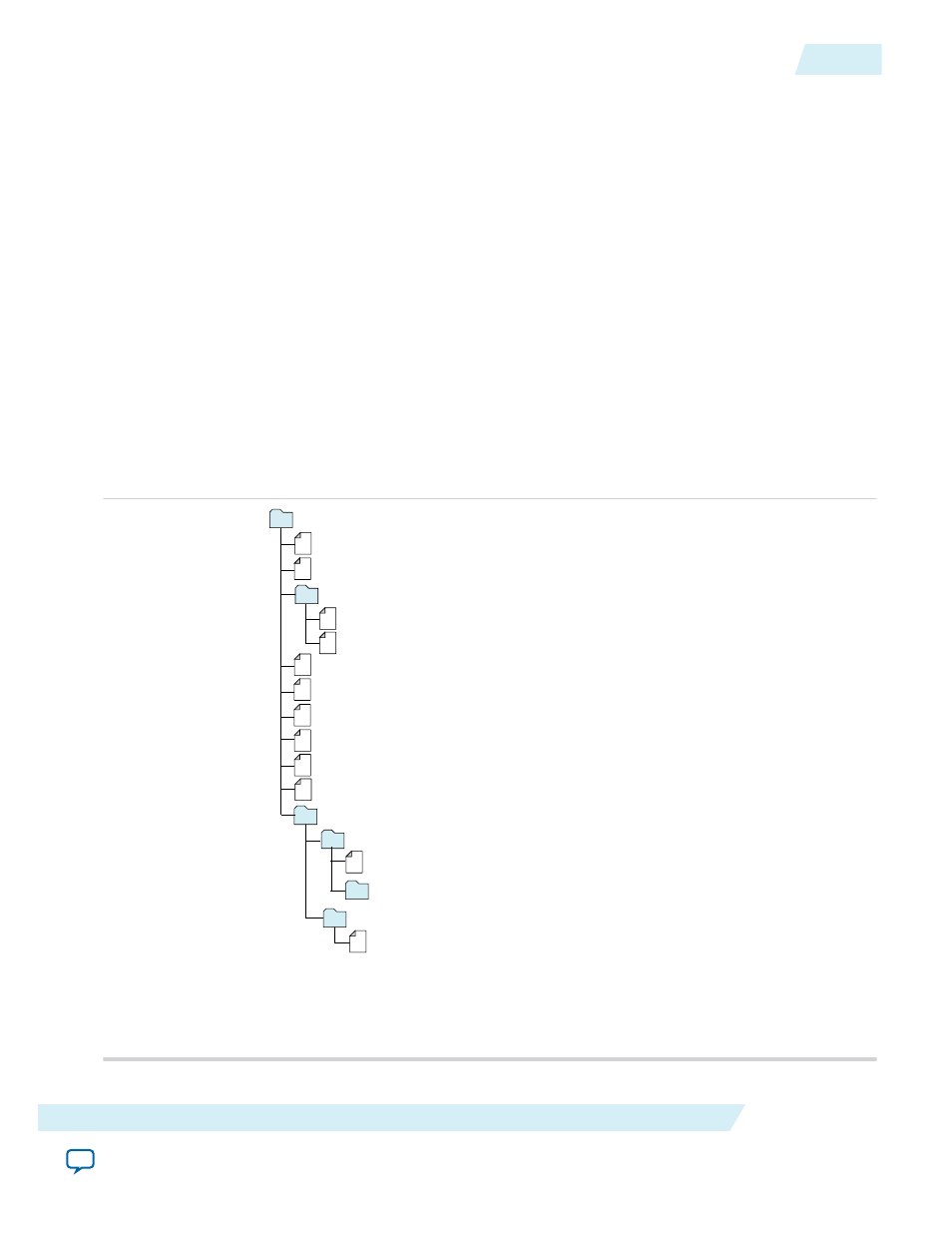

Figure 2-2: IP Core Generated Files

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

3. If example design is generated

<Project Directory>

<your_ip>_sim 1

ilk_core.sv - IPFS model 2

<simulator_vendor>

<simulator setup scripts>

<your_ip>.qip - Quartus II IP integration file

<your_ip>.sip - Lists files for simulation

<your_ip>.v, .sv. or .vhd - Top-level IP synthesis file

ilk_core

<your_ip>.cmp - VHDL component declaration file

<your_ip>.bsf - Block symbol schematic file

<your_ip> - IP core synthesis files

ilk_core.sv - HDL synthesis file

ilk_top.sdc - Timing constraints file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation scripts

1

<your_ip>_sim.f - Refers to simulation models and scripts

1

testbench

3

UG-01128

2015.05.04

Files Generated for Arria V GZ and Stratix V Variations

2-3

Getting Started With the 100G Interlaken IP Core

Altera Corporation