Altera 100G Interlaken MegaCore Function User Manual

Page 8

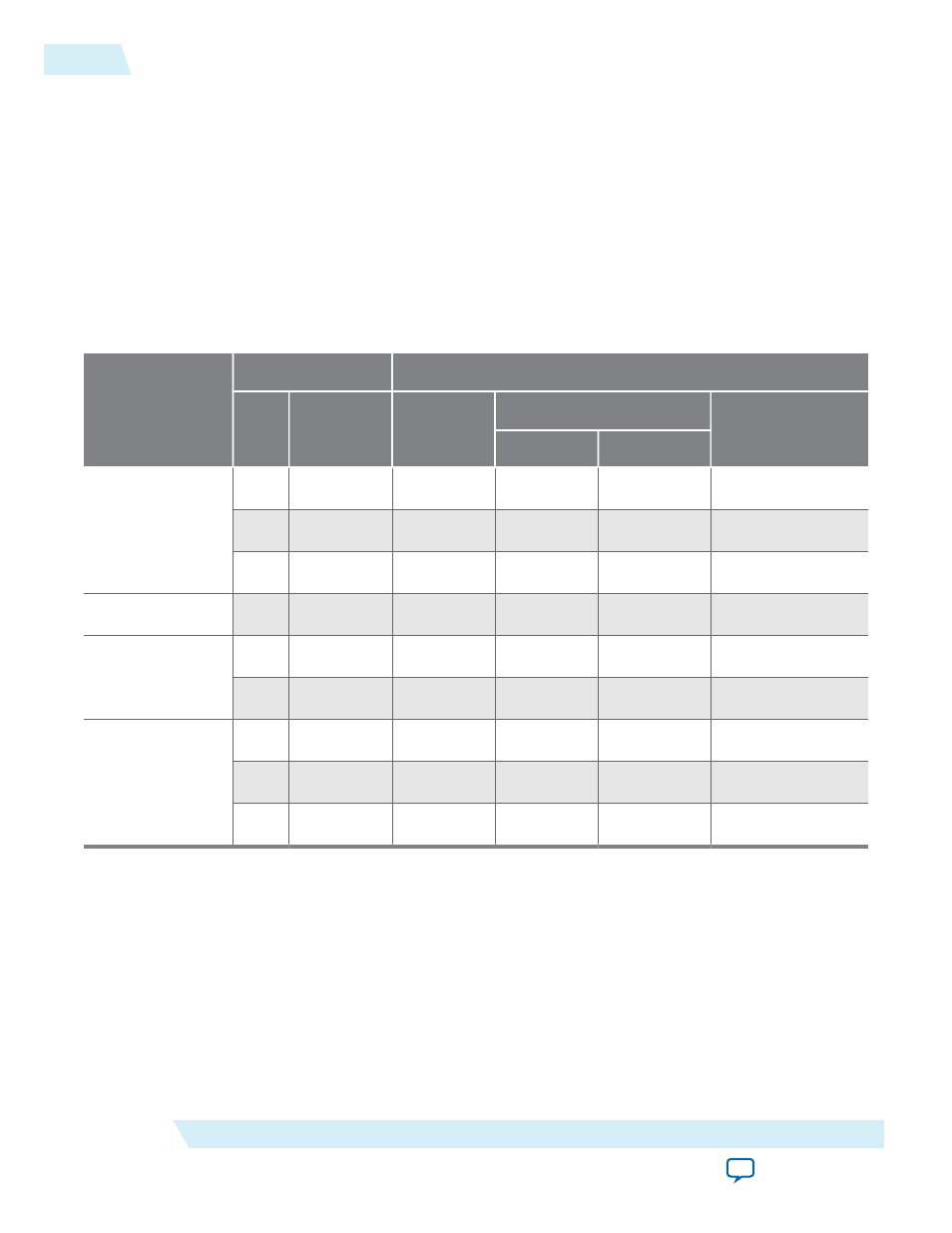

Table 1-5: 100G Interlaken MegaCore Function FPGA Resource Utilization

Lists the resources and expected performance for selected variations of the 100G Interlaken IP core using the

Quartus II software v13.1 and v13.1 Arria 10 edition releases for the following devices:

• Arria 10 device 10AX115S2F45I2SGES

• Arria V GZ device 5AGZE1H2F35I3

• Stratix V GX device 5SGXMA7N2F45I3

• Stratix V GT device 5SGTMC7K3F40I2

The results in this table do not include the out-of-band flow control block.

The numbers of ALMs and logic registers are rounded up to the nearest 100. The numbers of ALMs, before

rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

Device

Parameters

Resource Utilization

Numb

er of

Lanes

Per‑Lane

Data Rate

(Gbps)

ALMs

Needed

Logic Registers

M20K Blocks

Primary

Secondary

Arria 10

12

10.3125

17500

34100

1800

38

12

12.500

17600

34100

1900

38

24

6.25

26100

48500

3200

38

Arria V GZ

12

10.3125

17300

34100

2500

38

Stratix V GX

12

10.3125

17200

34200

2300

38

24

6.250

25100

47600

3200

38

Stratix V GT

12

10.3125

17200

34200

2400

38

12

12.500

17300

34100

2600

38

24

6.250

2500

47600

3100

38

Related Information

•

Information about Quartus II resource utilization reporting for 28-nm devices, including ALMs

needed.

•

Includes information about how to apply the Speed setting.

1-4

Performance and Resource Utilization

UG-01128

2015.05.04

Altera Corporation

About This MegaCore Function