Altera 100G Interlaken MegaCore Function User Manual

Page 107

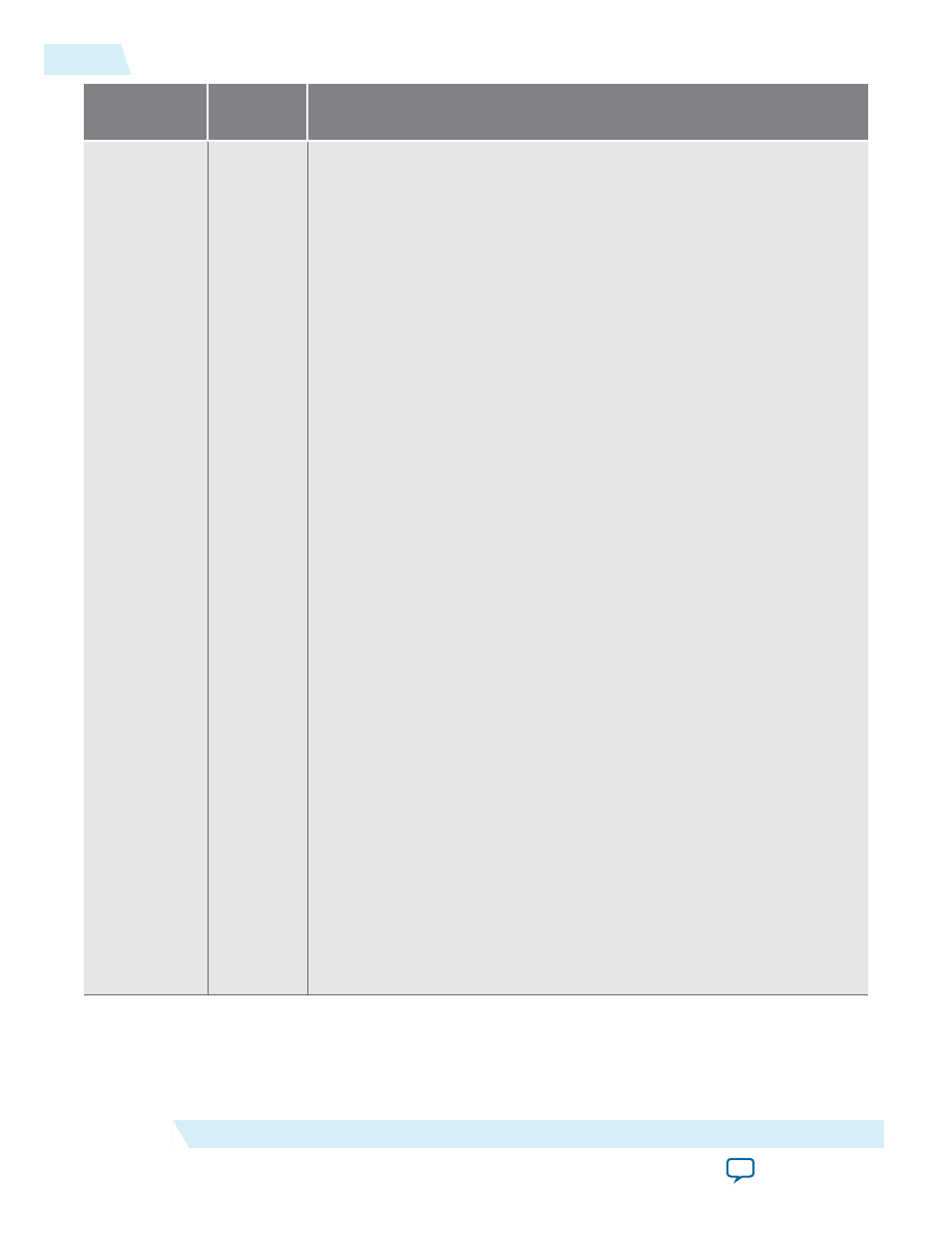

Date

ACDS

Version

Changes Made

2014.12.15

14.1

• Updated release-specific information for the software release v14.1,

including new resource utilization numbers and new Arria 10 speed

grade notation.

• Updated for new Quartus II IP Catalog, which replaces the MegaWizard

Plug-In Manager starting in the Quartus II software v14.0. Changes are

located primarily in Getting Started With the 100G Interlaken IP Core

chapter. Reordered the chapter to accommodate the new descriptions.

• Fixed speed grade information for Arria 10 devices in Device Speed

Grade Support section.

• Removed

mm_clk_locked

signal. Signal is removed in the IP core v14.0

and later.

• Corrected management interface read operation waveform and require‐

ments. In the IP core v13.1 and later, the read data is valid two cycles

after

mm_read

is asserted, not one cycle as was previously shown.

• Corrected instructions to connect the external TX PLL to include the

tx_

cal_busy

signal, and added example figure to illustrate the required

connections between the IP core and an ATX PLL. Changes are located in

Adding the External PLL section.

• In relevant parameter description sections, removed note to ignore the

compilation warnings if you turn off any of the following parameters.

The issue is fixed in the SDC file in the IP core version 14.0 and later.

• Include advanced error reporting and handling

• Enable M20K ECC support

• Include diagnostic features

• Include in-band flow control functionality

• Removed

CNTR_BITS

RTL parameter. Parameter is removed in the IP

core v14.0 and later.

• Added information to IP Core Reset section about the current required

wait from reset to successful register access in IP Core Reset section.

• Corrected width of

reconfig_waitrequest

signal to one bit. This signal

has been a single bit in all versions that support Arria 10 devices, starting

with the IP core version 13.1 Arria 10 Edition.

• Corrected the text that describes the trade-offs between enabling and

disabling the Enable M20K ECC support parameter.

• Added information about turning on and off loopback mode in two new

sections, External Loopback Mode and Internal Serial Loopback Mode, in

IP Core Test Features chapter.

• Clarified that the testbench and example design are generated only if you

specify the IP core synthesis and simulation models are in Verilog HDL.

The IP core does not support VHDL models, despite the fact that in the

IP core v14.0 and later, the parameter editor appears to offer that option.

• Fixed assorted typos and formatting issues.

B-2

Document Revision History

UG-01128

2015.05.04

Altera Corporation

Additional Information