Altera 100G Interlaken MegaCore Function User Manual

Page 75

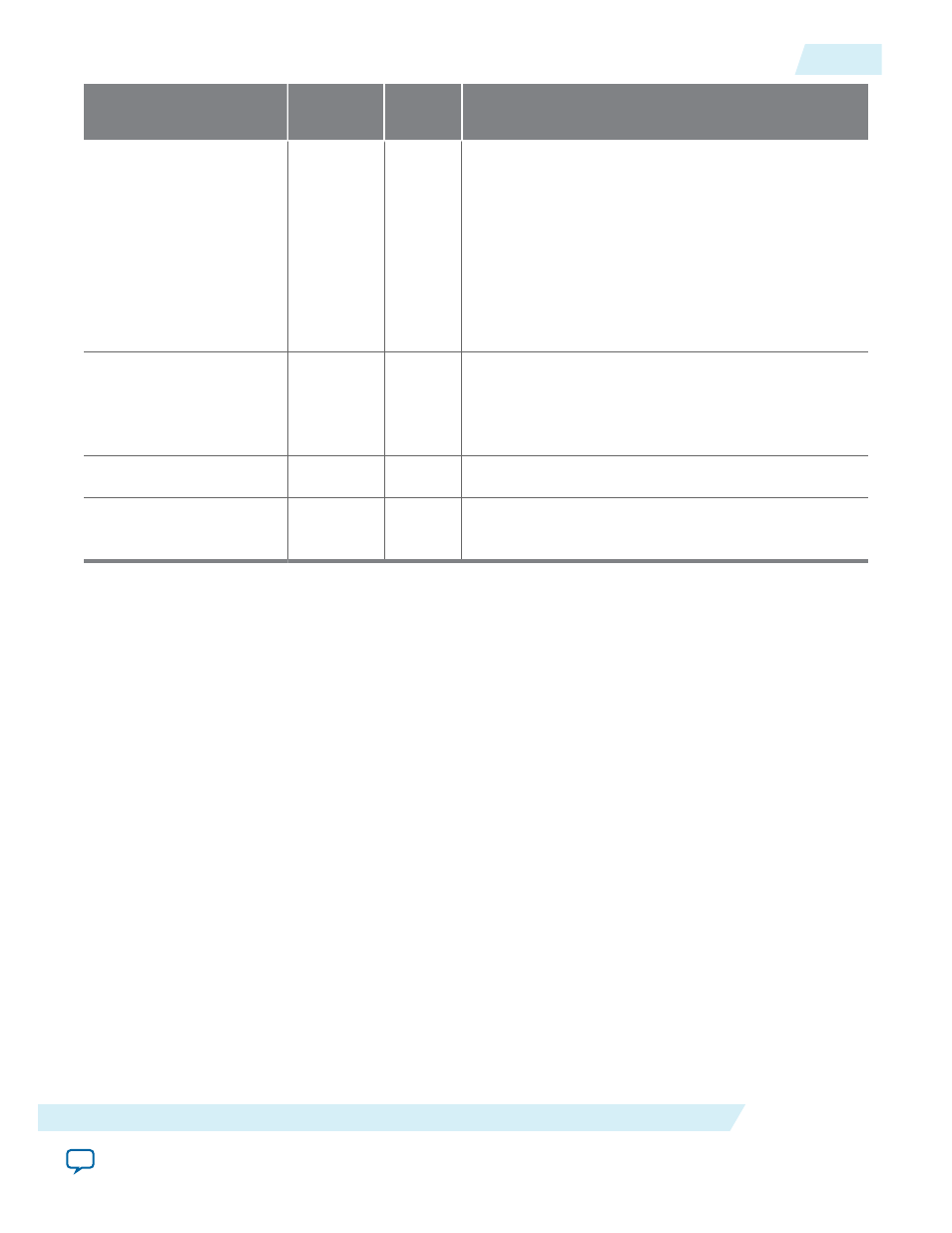

Signal Name

Direction

Width

(Bits)

Description

reconfig_address

Input

14 or 15 Address to access the hard PCS registers. This signal

holds both the hard PCS register offset and the

transceiver channel being addressed, in the following

fields:

• [8:0]: register offset in the hard PCS

• [N:9]: Interlaken lane number

• In 12-lane variations, N is 13

• In 24-lane variations, N is 14

reconfig_readdata

Output

32

After user logic asserts the

reconfig_read

signal,

when the IP core deasserts the

reconfig_

waitrequest

signal,

reconfig_readdata

holds valid

read data.

reconfig_waitrequest

Output

1

Busy signal for

reconfig_readdata

.

reconfig_writedata

Input

32

When

reconfig_write

is high,

reconfig_writedata

holds valid write data.

Related Information

Defines the Avalon-MM interface specification, including the behavior of the output signals and the

expected behavior of the input signals.

UG-01128

2015.05.04

Arria 10 Transceiver Reconfiguration Interface Signals

5-17

100G Interlaken MegaCore Function Signals

Altera Corporation